Lvds display color mapping tables – Kontron COMe Starterkit Eval T2 User Manual

Page 95

COM Express Interfaces

The Open LDI specification uses the term “pixel clock” differently from most other documents. In

the Open LDI specification, the “pixel clock” period is seven pixel periods long. Most other

documents refer to this concept as the “LVDS clock.”

Transmit Bit Order

In this document, the seven bits in an LVDS frame are numbered 1 – 7, with Bit 1 being placed

into the stream before Bit 2.

Display terms used in this document are defined in Table 28 above.

2.11.1.6.

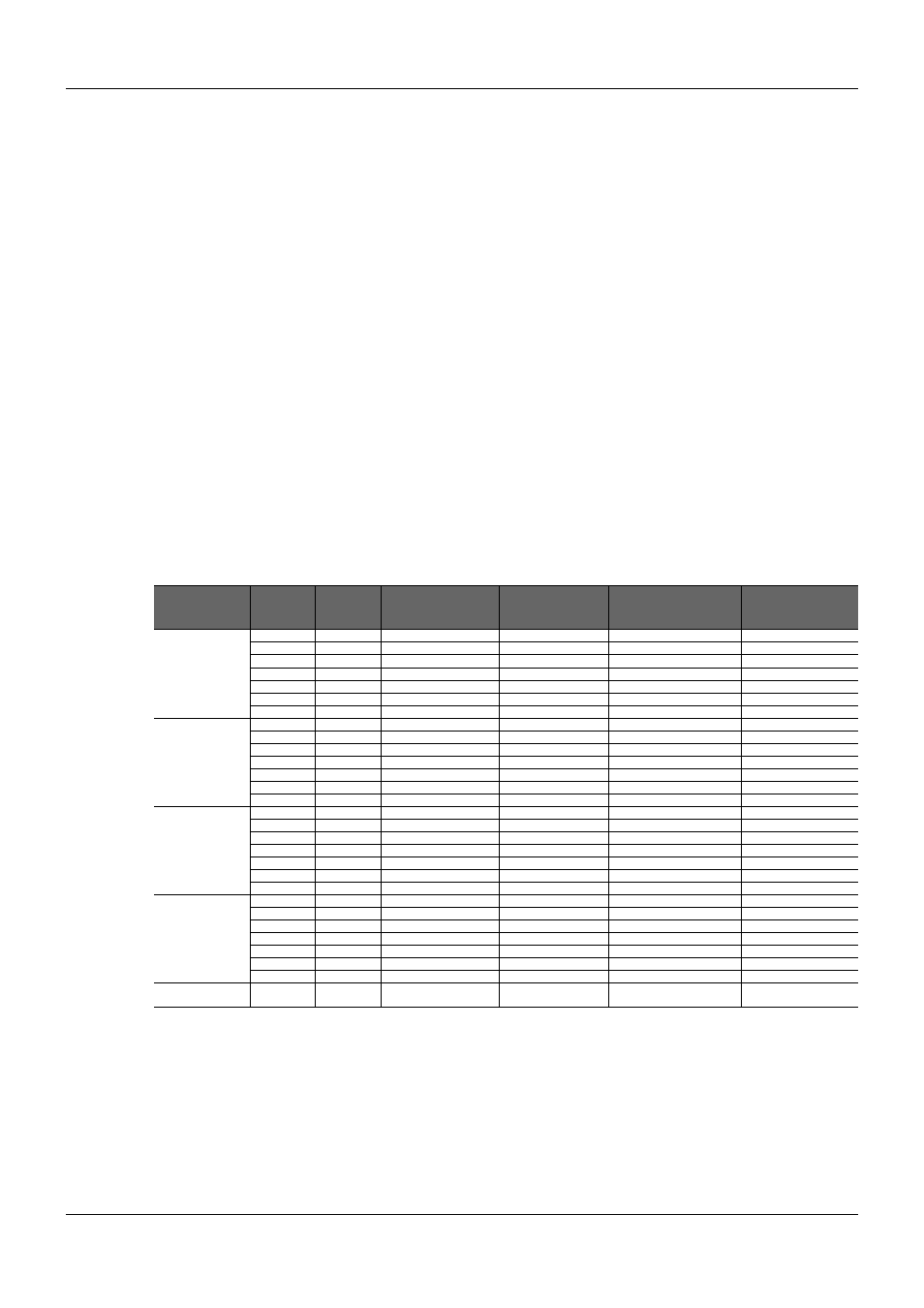

LVDS Display Color Mapping Tables

LVDS display color-mappings for single- and dual-channel displays are shown in Table 29 and

Table 30 below.

For single-channel displays, COM Express Module LVDS B pairs are not used and may be left

open. For single-channel, 18-bit displays, the LVDS_A3± channel is not used and may be left

open.

For 18-bit, single-channel and 36-bit, dual-channel displays, the FPD-Link and Open LDI color-

mappings are the same. For 24-bit, single-channel and 48-bit, dual-channel displays, mappings

differ and care must be taken that the Module and display LVDS color-mappings agree.

Table 29:

LVDS Display: Single Channel, Unbalanced Color-Mapping

Xmit

Bit

Order

LVDS

Clock

Open LDI

18 bit

Single Ch

Open LDI

24 bit

Single Ch

FPD Link

18 bit

Single Ch

FPD Link

24 bit

Single Ch

LVDS_A0±

1

1

G0

G2

G0

G0

2

1

R5

R7

R5

R5

3

0

R4

R6

R4

R4

4

0

R3

R5

R3

R3

5

0

R2

R4

R2

R2

6

1

R1

R3

R1

R1

7

1

R0

R2

R0

R0

LVDS_A1±

1

1

B1

B3

B1

B1

2

1

B0

B2

B0

B0

3

0

G5

G7

G5

G5

4

0

G4

G6

G4

G4

5

0

G3

G5

G3

G3

6

1

G2

G4

G2

G2

7

1

G1

G3

G1

G1

LVDS_A2±

1

1

DE

DE

DE

DE

2

1

VSYNC

VSYNC

VSYNC

VSYNC

3

0

HSYNC

HSYNC

HSYNC

HSYNC

4

0

B5

B7

B5

B5

5

0

B4

B6

B4

B4

6

1

B3

B5

B3

B3

7

1

B2

B4

B2

B2

LVDS_A3±

1

1

2

1

B1

B7

3

0

B0

B6

4

0

G1

G7

5

0

G0

G6

6

1

R1

R7

7

1

R0

R6

LVDS_A_CK±

LCLK = PCLK / 7

SCLK = PCLK

LCLK= PCLK / 7

SCLK = PCLK

LCLK = PCLK / 7

SCLK = PCLK

LCLK = PCLK / 7

SCLK = PCLK

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

95/218