Note on industry terms – Kontron COMe Starterkit Eval T2 User Manual

Page 94

COM Express Interfaces

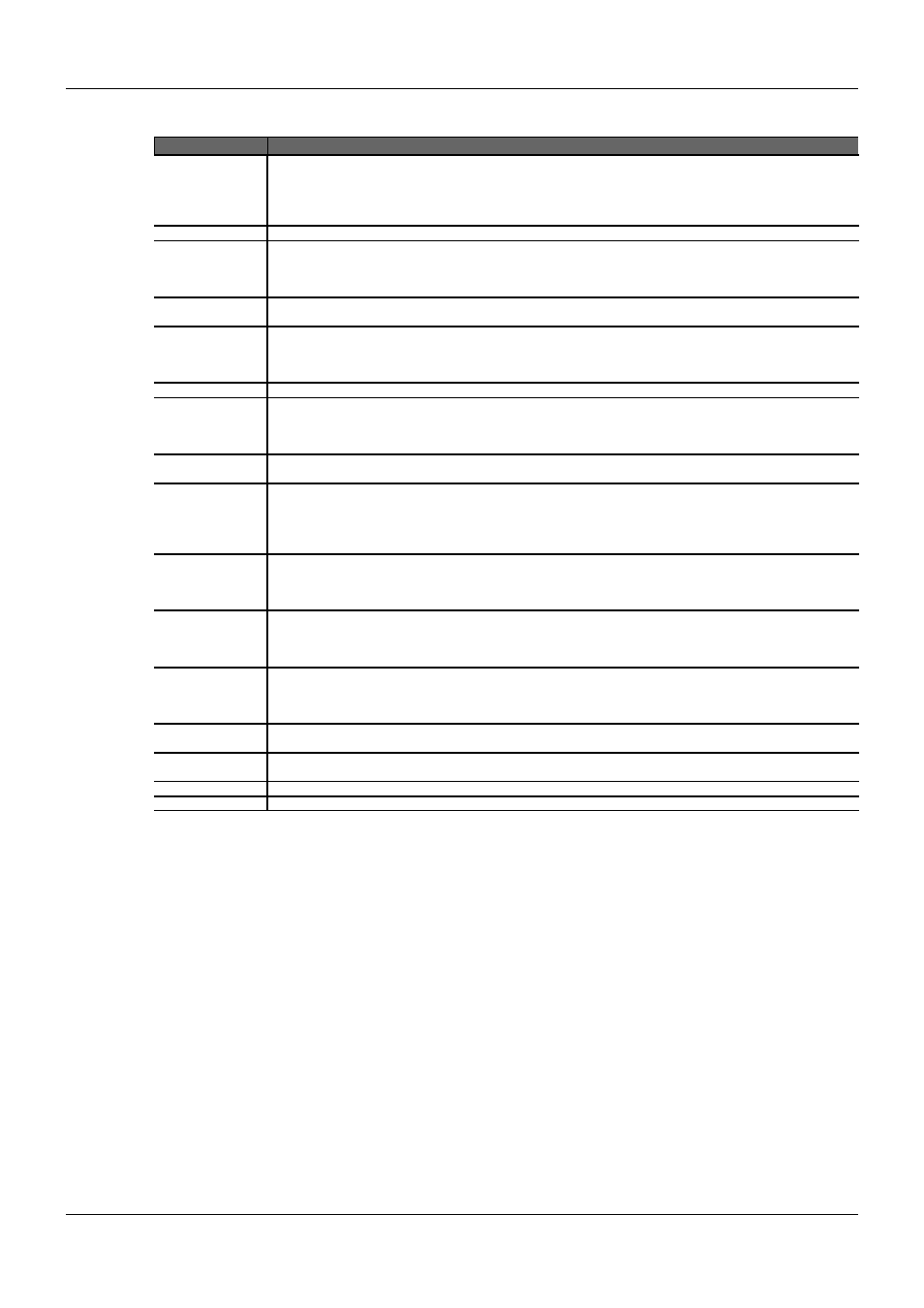

Table 28:

LVDS Display Terms and Definitions

Term

Definition

Color-Mapping

Color-mapping refers to the order in which display color bits and control bits are placed into the serial

LVDS stream. Each LVDS data frame can accept seven bits. The way in which the bits are serialized

into the stream is arbitrary, as long as they are de-serialized in a corresponding way. Two main color-

mapping schemes are FPD-Link and Open LDI. They are the same for 18-bit panels but differ for 24-bit

panels.

DE

Display Enable – a control signal that asserts during an active display line.

Dual Channel

In a dual-channel bit stream, two complete RGB pixels are transmitted with each shift clock.

The shift clock is one half the pixel frequency in this case. Dual channel LVDS streams are either 8

differential pairs (6 data pairs, 2 clock pairs, for dual 18 bit streams) or 10 differential pairs (8 data pairs,

2 clock pairs, for dual 24-bit streams).

Even Pixel

A pixel from an even column number, counting from 1. For example, on an 800x600 display, the even

pixels along a row are in columns 2,4 … 800. The odd pixels are in columns 1,3,5 … 799.

FPD-Link

Flat Panel Display Link – an LVDS color-mapping scheme popularized by National Semiconductor.

FPD Link color-mapping is the same as open LDI color-mapping for 18-bit displays but is different for

24-bit displays. FPD color-mapping puts the most significant bits of a 24-bit display onto the 4

th

LVDS

channel.

HSYNC

Horizontal Sync – a control signal that occurs once per horizontal display line.

LCLK

LVDS clock – the low voltage differential clock that accompanies the serialized LVDS data stream. For

a single-channel LVDS stream, the LVDS clock is 1/7

th

the pixel clock, which means there is one LVDS

clock period for every 7 pixel clock periods. For a dual-channel LVDS data stream, the LVDS clock is

1/14

th

the pixel clock, which means there is one LVDS clock period for every 14-pixel clock periods.

Odd Pixel

A pixel from an odd column number, counting from 1. For example, on an 800x600 display, the odd

pixels along a row are in columns 1,3,5, … 799. The even pixels are in columns 2,4 …800.

Open LDI

Open LVDS Display Interface – a formalization by National Semiconductor of de facto LVDS standards.

See Appendix G for a reference to the standard. Open LDI color-mapping is the same as FPD-Link

color-mapping for 18-bit displays, but is different for 24-bit displays. Open LDI color-mapping puts the

least significant bits of a 24-bit display onto the 4

th

LVDS channel. Doing so means that an 18-bit

display can operate on a 24-bit Open LDI link by using the first 3 LVDS data channels.

PCLK

Pixel clock – the clock associated with a single display pixel. For example, on a 640x480 display, there

are 640 pixel clocks during the active display line period (and additional pixel clocks during the blanking

periods). For a single-channel TFT display, the pixel clock is the same as the shift clock. For a dual-

channel TFT display, the pixel clock is twice the frequency of the shift clock.

SCLK

Shift clock – the clock that shifts either a single pixel or a group of pixels into the display, depending on

the display type. For a single-channel TFT display, the shift clock is the same as the pixel clock. For a

dual-channel TFT display, the shift clock period is twice the pixel clock. For some display types, such

as passive STN displays, the shift clock may be four- or eight-pixel clocks.

Single Channel

In a single-channel bit stream, a single RGB pixel is transmitted with each shift clock. The shift clock

and the pixel clock are the same in this case. Single-channel LVDS streams are either 4 differential

pairs (3 data pairs, 1 clock pair, for a single 18 bit stream) or 5 differential pairs (4 data pairs, 1 clock

pair, for a single 24-bit stream).

Transmit Bit

Order

The order, in time, in which bits are placed into the seven bit slots per LVDS frame.

Bit 1 is earlier in time than bit 2, etc.

Unbalanced

Unbalanced means that the LVDS serializing hardware does not insert or manipulate bits to achieve a

DC balance – i.e. an equal number of 0 and 1 bits, when averaged over multiple frames.

VSYNC

Vertical Sync – a control signal that occurs once per display frame.

Xmit Bit Order

See Transmit Bit Order.

2.11.1.5.

Note on Industry Terms

Some terms in this document that describe LVDS displays may vary from other documents (such

as display data sheets from vendors, IC data sheets for graphics controllers and LVDS

transmitters and receivers, the Open LDI specification, and COM Express Module

documentation).

Examples of terms that may vary include:

For dual-channel displays, terms are needed to describe the adjacent pixels.

Various documents will reference for the same pair of pixels:

Odd and Even pixels (column count starts at 1)

Even and Odd pixels (column count starts at 0)

R10 and R20 for adjacent least significant Red bits

R00 and R10 for adjacent least significant Red bits

Terms used to describe the clocks vary:

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

94/218