Com express interfaces, Picmg, Com express – Kontron COMe Starterkit Eval T2 User Manual

Page 35

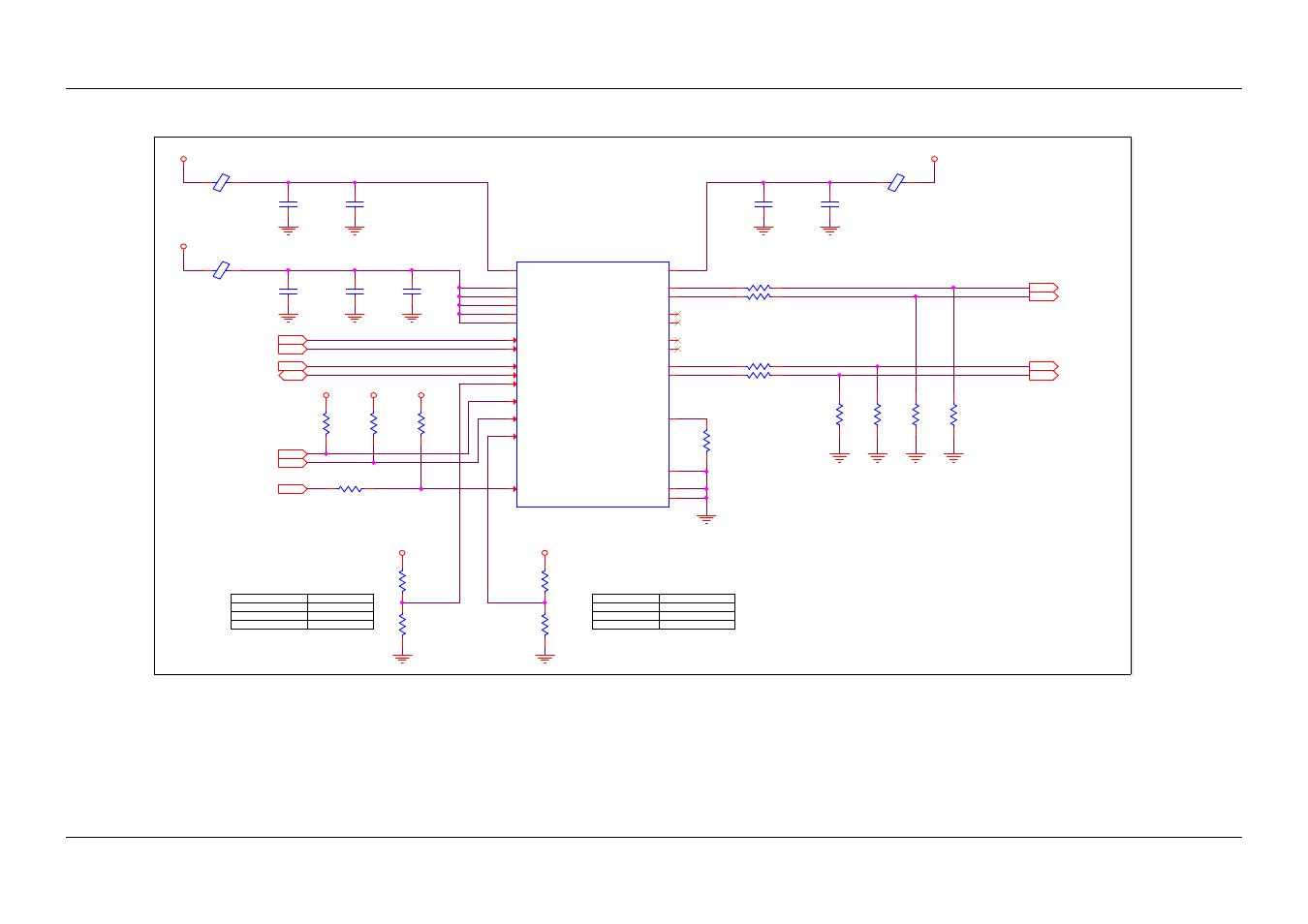

COM Express Interfaces

Figure 6:

PCIe Reference Clock Buffer

The following notes apply to Figure 6 'PCIe Reference Clock Buffer'.

Nets that tie directly to the COM Express connector are indicated with the CEX flag in the off-page connection symbol.

Each clock pair is routed point to point to each connector or end device using differential signal routing rules.

PICMG

®

COM Express

®

Carrier Board Design Guide Draft

Rev. 2.0 / December 6, 2013

35/218

OPEN

SMBus Addres selection

Assembled part

Address

R6

R5 + R6

R5

DA/DB

DC/DD

D8/D9

OPEN

PLL Operating mode selection

R7 + R8

R8

Mode

Assembled part

PLL 100M Lo BW

PLL 100M Hi BW

Bypass

R7

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

VCC_3V3

PCIE_CLK_REQ1#

PCIE_CLK_6+

PCIE_CLK_6-

PCIE_CLK_1+

PCIE_CLK_1-

PCIE_CLK_REQ6#

CEX

PCIE_CLK_REF+

CEX

PCIE_CLK_REF-

SMB_CK_S0

SMB_DAT_S0

CEX

SUS_S3#

C3

10uF

C6

10n

C2

100n

R1

47K

R7

10K

R6

10K

R4

0

FB1

120-Ohms@100MHz

R17

49.9

FB3

120-Ohms@100MHz

R13

475

R5

10K

FB2

120-Ohms@100MHz

R3

47K

R16

49.9

R12

33

R11

33

R15

49.9

R14

49.9

R10

33

R9

33

DIFFERENTIAL

CLOCK BUFFER

IDT9DB433

U1

VDD

5

VDD

11

VDD

16

VDD

18

VDDA

28

SRC_IN

2

SRC_IN#

3

SMBCLK

13

SMBDAT

14

IREF

26

GNDA

27

GND

15

GND

4

DIF_6

23

DIF_1

6

DIF_1#

7

BYP#_HIBW_LOBW

12

OE1#

8

PD#

25

VDD

24

VDDR

1

DIF_2

9

DIF_2#

10

DIF_5

20

DIF_5#

19

DIF_6#

22

OE6#

21

SMB_ADR_TRI

17

C5

10n

R2

47K

C4

100n

C1

10uF

R8

10K

C7

10uF