Lpc bus – low pin count interface, Signal definition, Lpc bus reference schematics – Kontron COMe Starterkit Eval T2 User Manual

Page 111: Lpc bus clock signal

COM Express Interfaces

2.16.

LPC Bus – Low Pin Count Interface

Since COM Express is designed to be a legacy free standard for embedded Modules, it does not

support legacy functionality on the Module, such as PS/2 keyboard/mouse, serial ports, and

parallel ports. Instead, it provides an LPC interface that can be used to add peripheral devices to

the Carrier Board design. COM Express also provides interface pins necessary for (optional)

Carrier Board resident PS keyboard controllers

The Low Pin Count Interface was defined by the Intel

®

Corporation to facilitate the industry's

transition toward legacy free systems. It allows the integration of low-bandwidth legacy I/O

components within the system, which are typically provided by a Super I/O controller.

Furthermore, it can be used to interface Firmware Hubs, Trusted Platform Module (TPM)

devices, general-purpose inputs and outputs, and Embedded Controller solutions. Data transfer

on the LPC bus is implemented over a 4 bit serialized data interface, which uses a 33MHz LPC

bus clock. It is straightforward to develop PLDs or FPGAs that interface to the LPC bus. A PLD

circuit example is given in Figure 43 'LPC PLD Example – Port 80 Decoder Schematic' below.

For more information about LPC bus, refer to the 'Intel

®

Low Pin Count Interface Specification

Revision 1.1'.

2.16.1.

Signal Definition

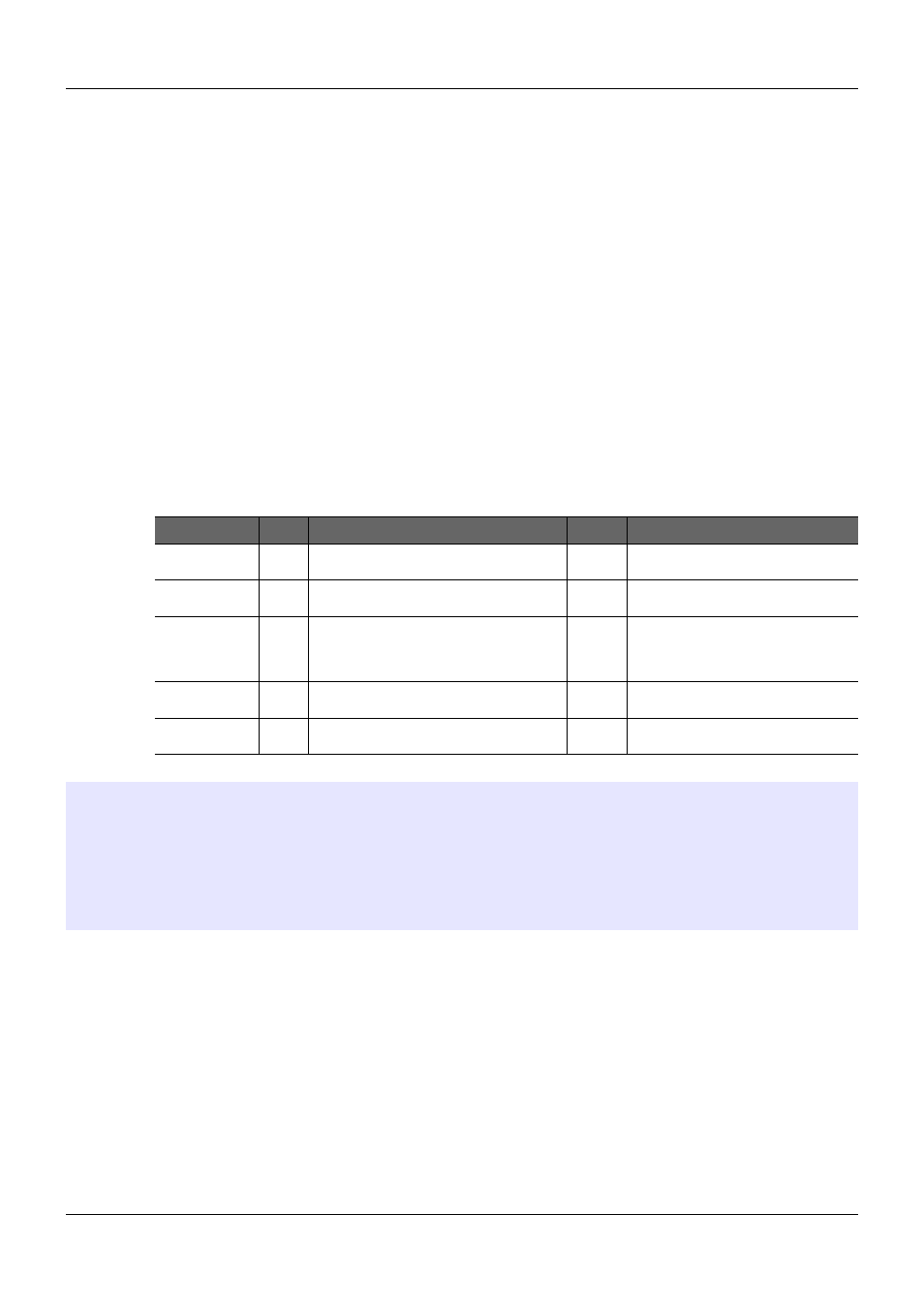

Table 34: LPC Interface Signal Descriptions

Signal

Pin

Description

I/O

Comment

LPC_SERIRQ

A50

LPC serialized IRQ.

I/O 3.3V

CMOS

LPC_FRAME#

B3

LPC frame indicates start of a new cycle or

termination of a broken cycle.

O 3.3V

CMOS

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

B4

B5

B6

B7

LPC multiplexed command, address and

data.

I/O 3.3V

CMOS

LPC_DRQ0#

LPC_DRQ1#

B8

B9

LPC encoded DMA/Bus master request.

I 3.3V

CMOS

Not all Modules support LPC DMA.

Contact your vendor for information.

LPC_CLK

B10

LPC clock output 33MHz.

O 3.3V

CMOS

Note

Implementing external LPC devices on the COM Express Carrier Board always

requires customization of the COM Express Module's BIOS in order to support

basic initialization for those LPC devices. Otherwise the functionality of the

LPC devices will not be supported by a Plug&Play or ACPI capable system.

See Section 4 'BIOS Considerations' on page 170 below for further information.

Contact your Module vendor for a list of specific SIO devices for which there

may be BIOS support.

2.16.2.

LPC Bus Reference Schematics

2.16.2.1.

LPC Bus Clock Signal

COM Express specifies a single LPC reference clock signal called 'LPC_CLK' on the Modules

connector at row B pin B10. Newer chipsets do not provide a free running LPC_CLK. The clock

is stopped and started on-the-fly. The clock is only active during LPC bus cycles. This kind of a

clock can cause problems when used with PLL based zero delay buffers which require a number

of clock cycles to lock onto the incoming clock before the output is active. The issue is that the

LPC_CLK is not active for enough cycles before the data is read/written to the LPC bus. The

result is that the target LPC device does not see an LPC_CLK and misses the LPC cycle.

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

111/218