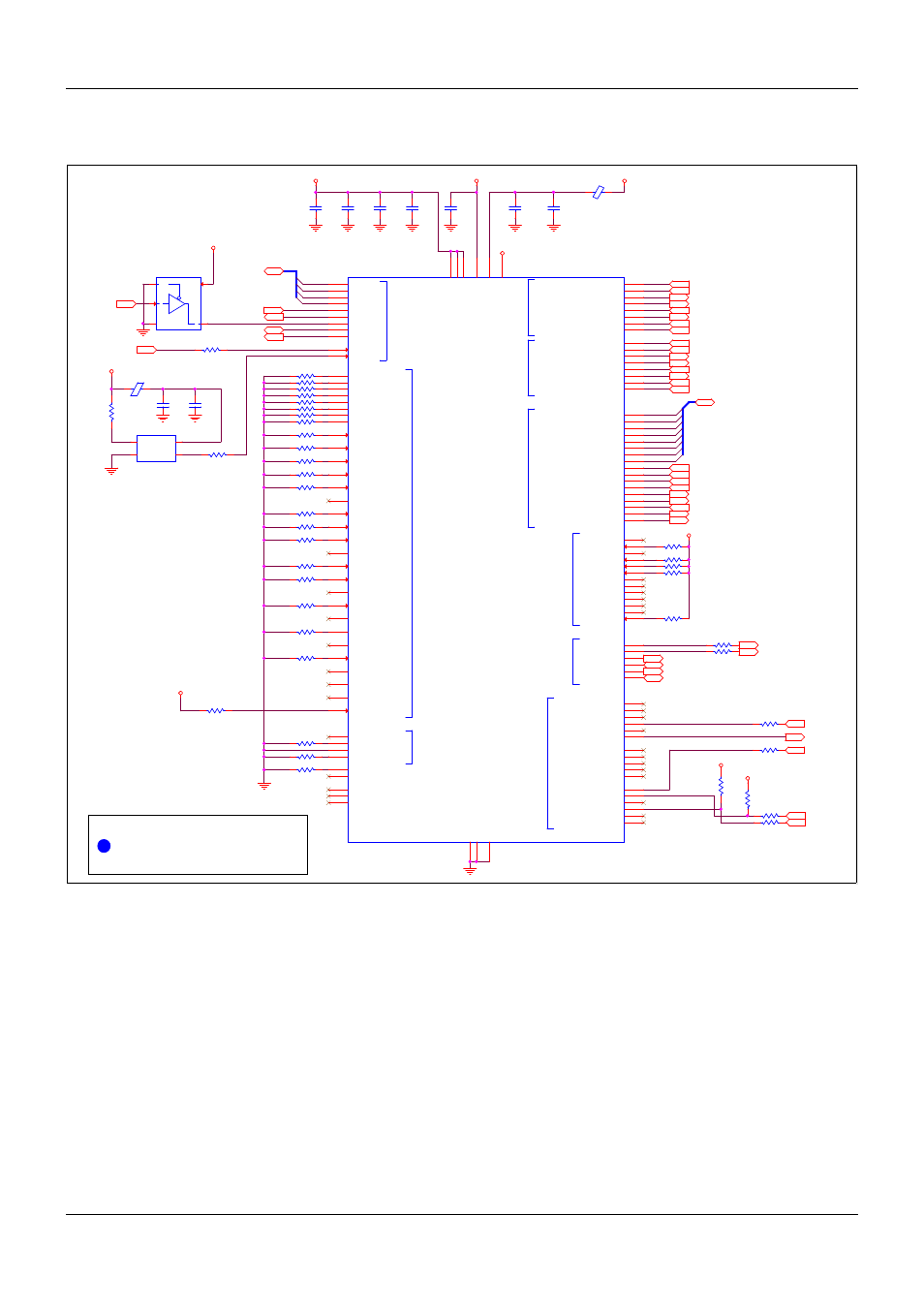

Superio, Super i/o, Superio figure 44: lpc super i/o example – Kontron COMe Starterkit Eval T2 User Manual

Page 115: Com express interfaces, Sio boot straps, Picmg, Com express

COM Express Interfaces

2.16.2.4.

SuperIO

Figure 44:

LPC Super I/O Example

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

115/218

SUPER I/O

Note: place series resistor near CEX connector

or use buffer for more than 2 LPC load

Note: Internal PD

SIO BOOT STRAPS

RTS0# => Default SIO Addr (2Eh) = 0, Alt SIO Addr (4Eh) = 1

DTR0# => Disable SPI = 0, Enable SPI = 1

TX0 => Disable Keyboard controller (KBC) = 0, Enable KBC = 1

TX1 => CPUFAN1 initial sped 100% = 0, CPUFAN1 initial sped 50% = 1

FAN_SET => CPUFAN0 initial sped 100% = 0, CPUFAN0 initial sped 50% = 1

EN_ACPI => Disable ACPI function = 0, Enable ACPI function = 0

SIO_WDT# => VID transition voltage TTL = 0, VID transition voltage GTL = 1

i

Signals KBD_A20GATE AND KBD_RST#

can be unconnected for completely legacy free system

SIO_SYS_RESET#

SIO_SUS_S5#

SIO_SUS_S3#

LPC_AD0

LPC_AD2

LPC_AD1

LPC_AD3

SIO_ATXPGD

TX0

CLK_48MHz

RTS0#

DTR0#

TX1

LPT_PD0

LPT_PD1

LPT_PD2

LPT_PD3

LPT_PD4

LPT_PD5

LPT_PD6

LPT_PD7

IO_RST#

V_BAT

VCC_3V3_STB

V_BAT

VCC_3V3_STB

VCC_3V3

VCC_3V3

VCC_3V3_SBY

VCC_3V3

VCC_3V3

VCC_3V3

CEX

LPC_SERIRQ

CEX

LPC_FRAME#

MCLK

KCLK

MDAT

KDAT

LPT_SLCT

LPT_PE

LPT_BUSY

LPT_ACK#

LPT_SLIN#

LPT_INIT#

LPT_STB#

LPT_ERR#

LPT_AFD#

CEX

SYS_RESET#

CEX

LPC_DRQ0#

CEX

SUS_S3#

CEX

SUS_S5#

CEX

PWR_OK

CEX

LPC_AD[0:3]

CEX

PWR_OK

TX0

RTS0#

DTR0#

CTS0#

DSR0#

RX0

DCD0#

RI0#

TX1

DTR1#

RTS1#

CTS1#

DSR1#

RX1

DCD1#

RI1#

CEX

PCI_PME#

LPT_PD[0:7]

CEX

CB_RESET#

CEX

LPC_CLK

CEX

KBD_A20GATE

CEX

KBD_RST#

R208

4k7

R191

0R

R200

0R

Y4

48MHz / 50ppm

OE

1

GND

2

OUT

3

VCC

4

R223

4k7

R443

2M

C237

1u

R229

4k7

R212

4k7

R363

10k

DNI

FB47

120R@100MHz

R226

4k7

R224

4k7

U30

74125

OE#

1

A

2

GND

3

Y

4

VCC

5

C243

100n

C246

100n

R222

4k7

R205

33R

R216

4k7

R219

4k7

FB57

120R / 0.2A

R209

4k7

R214

4k7

R228

4k7

R225

4k7

R193

0R 5%

R448

R221

4k7

R231

4k7

R227

4k7

R194

R451

1k

R204

10k

C247

22u

C238

10n

R207

22R

R211

4k7

R445

R447

R444

1k

R446

C242

100n

C245

100n

R218

4k7

R217

4k7

R230

4k7

C244

22u

R215

4k7

R213

4k7

R220

4k7

R210

4k7

W83627DHG

PQFP 128

LP

C

I/

F

HA

RD

WA

RE

M

ON

IT

OR

I

/F

PE

CI

I

/F

AC

P

I

KE

YB

OA

RD

/

M

OU

SE

FL

OO

PY

PA

RA

LL

EL

P

OR

T

SE

RI

AL

P

OR

T

B

SE

RI

AL

P

OR

T

A

U28

W83627DHG-P

G

N

D

1

20

LAD3

24

LAD2

25

G

N

D

2

55

LAD1

26

LAD0

27

LFRAME#

29

LDRQ#

22

SERIRQ

23

PME#

86

LRESET#

30

IOCLK

18

PCICLK

21

RIA#/GP60

57

DCDA#/GP61

56

SOUTA/GP62/PENKBC

54

SINA/GP63

53

DTRA#/GP64/PENROM

52

RTSA#/GP65/HEFRAS

51

DSRA#/GP66

50

CTSA#/GP67

49

RIB#/GP40

85

DCDB#/GP41

84

SOUTB/GP42/IRTX/FAN_SET2

83

SINB/GP43/IRRX

82

DTRB#/GP44

81

RTSB#/GP45

80

DSRB#/GP46

79

CTSB#/GP47

78

PD0/INDEX2#

42

PD1/TRAK02#

41

PD2/WP2#

40

PD3/RDATA2#

39

PD4/DSKCHG2#

38

PD5

37

PD6/MOA2#

36

PD7/DSA2#

35

SLCT/WE2#

31

PE/WD2#

32

BUSY/MOB2#

33

ACK#/DSB2#

34

SLIN#/STEP2#

43

INIT#/DIR2#

44

ERR#/HEAD2#

45

AFD#/DRVDEN02

46

STB#

47

DRVDEN0

1

DSKCHG#

17

HEAD#

16

RDATA#

15

WP#

14

TRAK0#

13

WE#

11

WD#

10

STEP#

9

DIR#

8

DSA#

6

MOA#

4

INDEX#

3

KDAT/GP26

63

KBRST#

60

GA20M

59

KCLK/GP27

62

MDAT/GP24

66

MCLK/GP25

65

V

B

A

T

74

PSIN#/GP56

68

PSOUT#/GP57

67

VID0

128

VID1

127

VID2

126

VID3

125

VID4

124

CASEOPEN#

76

SMI#/OVT#

5

VREF

101

AUXTIN

102

CPUVCORE

100

3V

C

C

_1

12

3V

C

C

_3

48

3V

C

C

_2

28

A

V

C

C

95

A

G

N

D

10

5

3V

S

B

61

RSTOUT1#

93

RSTOUT0#

94

SUSB#/GP52

73

PSON#/GP53

72

RSMRST#/GP51

75

VID5

123

VID6

122

VID7

121

VIN0

99

VIN1

98

VIN2

97

VIN3

96

CPUTIN

103

SYSTIN

104

SI/AUXFANIN1

58

AUXFANOUT

7

AUXFANIN0

111

CPUFANIN0

112

CPUFANOUT0

115

GP21/CPUFANIN1

119

GP20/CPUFANOUT1

120

SYSFANIN

113

SYSFANOUT

116

FAN_SET/PLED

117

BEEP/SO

118

PECI_REQ#

110

PECI

108

Vtt

107

PECISB

106

SST

114

NC1

109

PWROK/GP54

71

RSTOUT2#/GP32/SCL

90

RSTOUT3#/GP33/SDA

89

RSTOUT4#/GP34

88

SUSC#/GP37

64

FPTRST#/GP36

69

VSBGATE#/GP31

91

ATXPGD/GP35

87

EN_ACPI/GP55/SUSLED

70

PWROK2/GP30

92

SCK/GP23

2

SCE#/GP22

19

WDTO#/GP50/EN_GTL

77

C241

100n

R291

R292

0R

0R