Ide and compactflash (pata), Signal definitions – Kontron COMe Starterkit Eval T2 User Manual

Page 153

COM Express Interfaces

2.24.

IDE and CompactFlash (PATA)

2.24.1.

Signal Definitions

Type 2 and 4 COM Express Modules provide a single channel IDE interface supporting two

standard IDE hard drives or ATAPI devices with a maximum transfer rate of ATA100 (Ultra-DMA-

100 with 100MB/s transfer rate). The corresponding signals can be found on the Module

connector rows C and D.

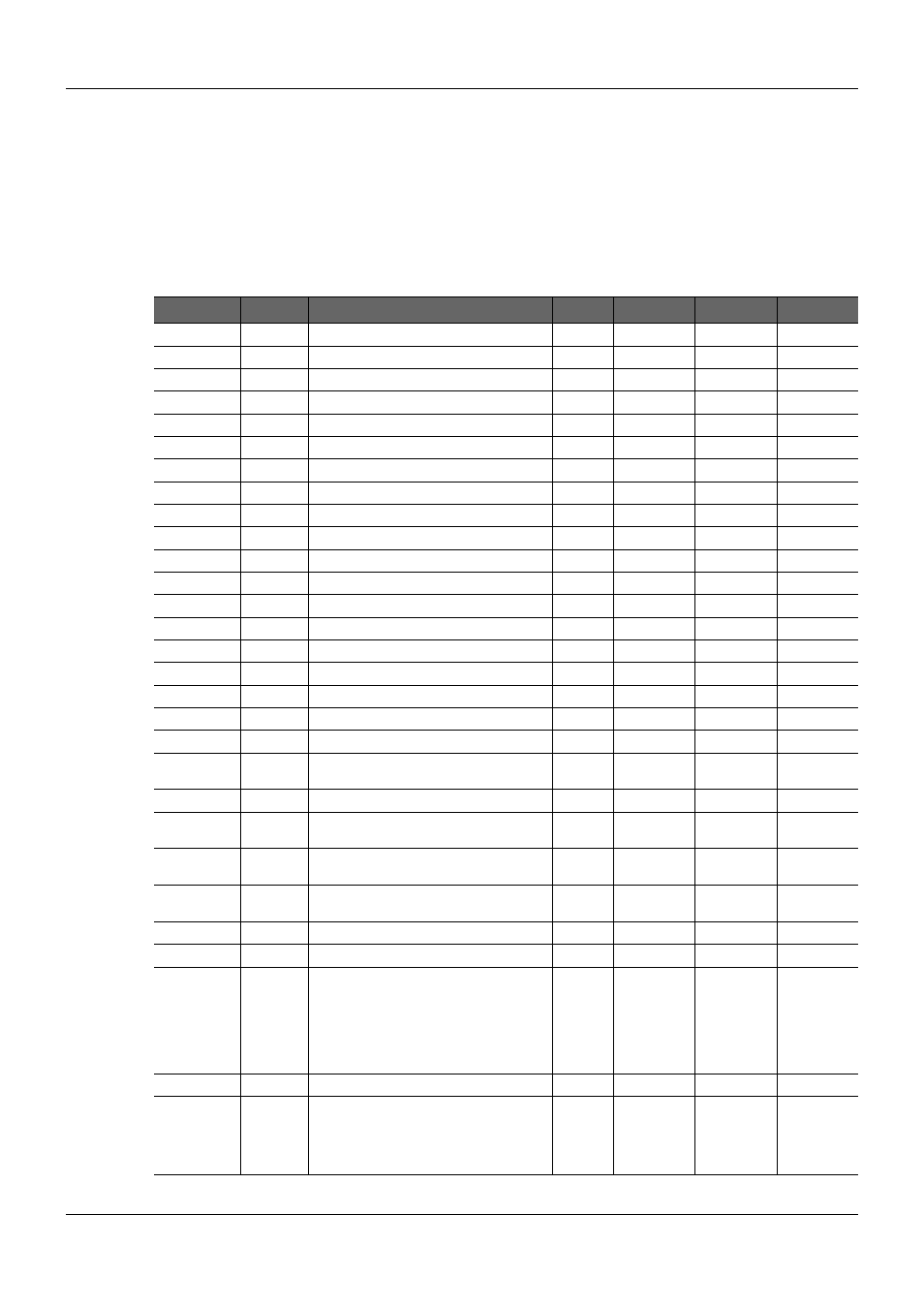

Table 50:

Parallel ATA Signal Descriptions

Signal

Pin

Description

I/O

IDE40

IDE44

CF

IDE_D0

D7

Bidirectional data to / from IDE device.

I/O 3.3V

17

17

21

IDE_D1

C10

Bidirectional data to / from IDE device.

I/O 3.3V

15

15

22

IDE_D2

C8

Bidirectional data to / from IDE device.

I/O 3.3V

13

13

23

IDE_D3

C4

Bidirectional data to / from IDE device.

I/O 3.3V

11

11

2

IDE_D4

D6

Bidirectional data to / from IDE device.

I/O 3.3V

9

9

3

IDE_D5

D2

Bidirectional data to / from IDE device.

I/O 3.3V

7

7

4

IDE_D6

C3

Bidirectional data to / from IDE device.

I/O 3.3V

5

5

5

IDE_D7

C2

Bidirectional data to / from IDE device.

I/O 3.3V

3

3

6

IDE_D8

C6

Bidirectional data to / from IDE device.

I/O 3.3V

4

4

47

IDE_D9

C7

Bidirectional data to / from IDE device.

I/O 3.3V

6

6

48

IDE_D10

D3

Bidirectional data to / from IDE device.

I/O 3.3V

8

8

49

IDE_D11

D4

Bidirectional data to / from IDE device.

I/O 3.3V

10

10

27

IDE_D12

D5

Bidirectional data to / from IDE device.

I/O 3.3V

12

12

28

IDE_D13

C9

Bidirectional data to / from IDE device.

I/O 3.3V

14

14

29

IDE_D14

C12

Bidirectional data to / from IDE device.

I/O 3.3V

16

16

30

IDE_D15

C5

Bidirectional data to / from IDE device.

I/O 3.3V

18

18

31

IDE_A[0:2]

D13-D15

Address lines to IDE device.

O 3.3V

35, 33, 36

35, 33, 36

20, 19, 18

IDE_IOW#

D9

I/O write line to IDE device.

O 3.3V

23

23

35

IDE_IOR#

C14

I/O read line to IDE device.

O 3.3V

25

25

34

IDE_REQ

D8

IDE device DMA request. It is asserted by

the IDE device to request a data transfer.

I 3.3V

21

21

37

IDE_ACK#

D10

IDE device DMA acknowledge.

O 3.3V

29

29

44

IDE_CS1#

D16

IDE device chip select for 1F0h to 1FFh

range.

O 3.3V

37

37

7

IDE_CS3#

D17

IDE device chip select for 3F0h to 3FFh

range.

O 3.3V

38

38

32

IDE_IORDY

C13

IDE device I/O ready input. Pulled low by

the IDE device to extend the cycle.

I 3.3V

27

27

42

IDE_RESET# D18

Reset output to IDE device, active low.

O 3.3V

1

1

41

IDE_IRQ

D12

Interrupt request from IDE device.

I 3.3V

31

31

43

IDE_CBLID#

D77

Input from off-Module hardware indicating

the type of IDE cable being used. High

indicates a 40-pin cable used for legacy

IDE modes. Low indicates that an 80-pin

cable with interleaved grounds is used.

Such a cable is required for Ultra-DMA 66,

100 modes.

I 3.3V

34

34

46

DASP

39

39

45

GND

2, 19, 22, 24,

26, 30, 40

2, 19, 22, 24,

26, 30, 40,

43

17, 16, 15,

14, 12, 11,

10, 8, 12, 6,

9, 33, 25, 26

39 (master)

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

153/218