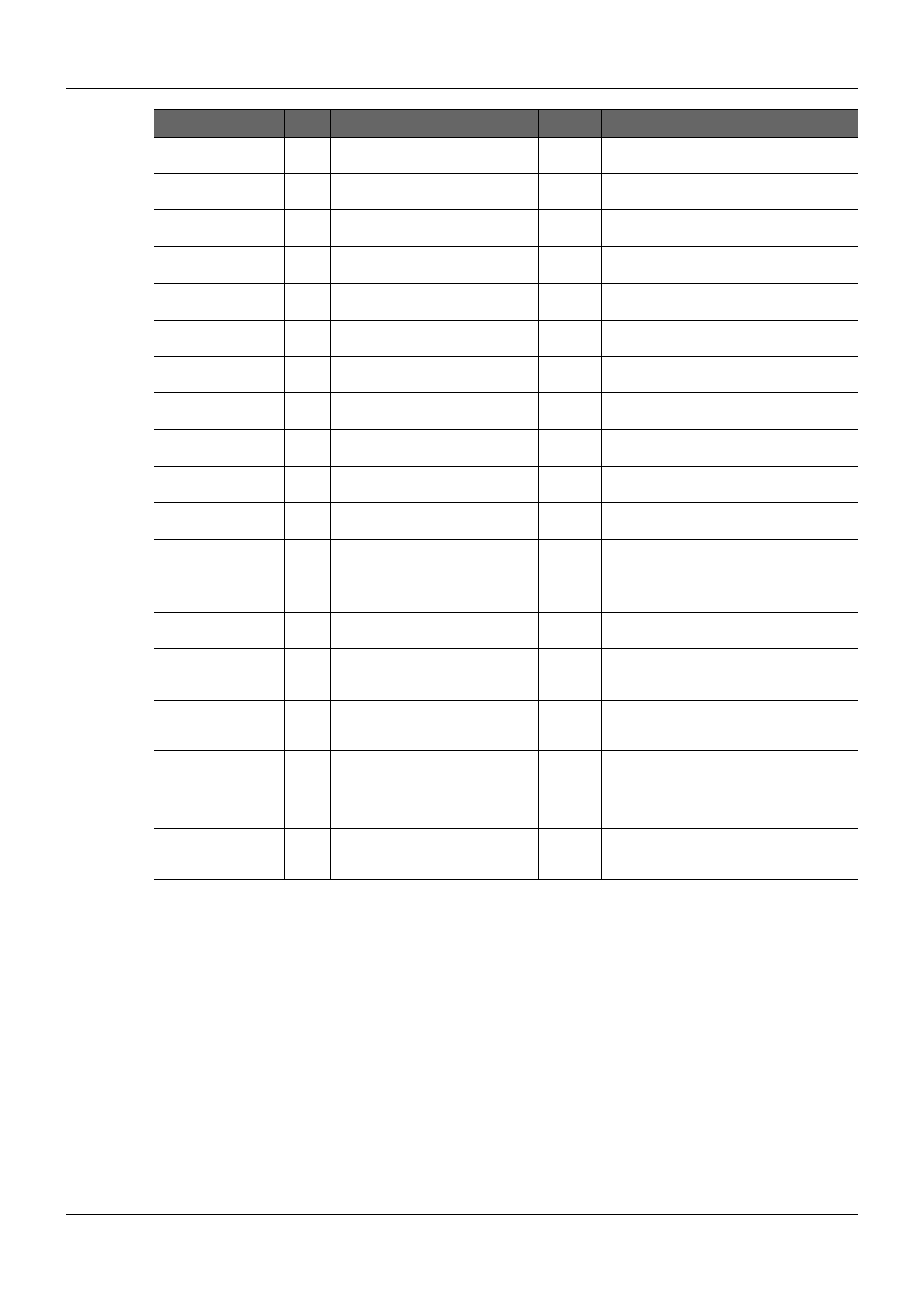

Peg configuration, Signal pin# description i/o comment – Kontron COMe Starterkit Eval T2 User Manual

Page 49

COM Express Interfaces

Signal

Pin# Description

I/O

Comment

PEG_TX9+

PEG_TX9-

D81

D82

PEG channel 9, Transmit Output

differential pair.

O PCIE

PEG_RX10+

PEG_RX10-

C85

C86

PEG channel 10, Receive Input

differential pair.

I PCIE

PEG_TX10+

PEG_TX10-

D85

D86

PEG channel 10, Transmit Output

differential pair.

O PCIE

PEG_RX11+

PEG_RX11-

C88

C89

PEG channel 11, Receive Input

differential pair.

I PCIE

PEG_TX11+

PEG_TX11-

D88

D89

PEG channel 11, Transmit Output

differential pair.

O PCIE

PEG_RX12+

PEG_RX12-

C91

C92

PEG channel 12, Receive Input

differential pair.

I PCIE

PEG_TX12+

PEG_TX12-

D91

D92

PEG channel 12, Transmit Output

differential pair.

O PCIE

PEG_RX13+

PEG_RX13-

C94

C95

PEG channel 13, Receive Input

differential pair.

I PCIE

PEG_TX13+

PEG_TX13-

D94

D95

PEG channel 13 Transmit Output

differential pair.

O PCIE

PEG_RX14+

PEG_RX14-

C98

C99

PEG channel 14, Receive Input

differential pair.

I PCIE

PEG_TX14+

PEG_TX14-

D98

D99

PEG channel 14, Transmit Output

differential pair.

O PCIE

PEG_RX15+

PEG_RX15-

C101

C102

PEG channel 15, Receive Input

differential pair.

I PCIE

PEG_TX15+

PEG_TX15-

D101

D102

PEG channel 15, Transmit Output

differential pair.

O PCIE

SDVO_I2C_CLK

D73

I2C based control signal (clock) for

SDVO device.

O 2.5V

CMOS

SDVO enabled if this line is pulled up to

2.5V on Carrier or on ADD2 (Type 2 only)

SDVO_I2C_DATA

C73

I2C based control signal (data) for

SDVO device

I/O 2.5V

OD

CMOS

SDVO enabled if this line is pulled up to

2.5V on Carrier or on ADD2 (Type 2 only)

PEG_LANE_RV#

D54

PCI Express Graphics lane reversal

input strap. Pull low on the carrier

board to reverse lane order.

I 3.3V

CMOS

PEG_ENABLE#

D97

PEG enable function. Strap to

enable PCI Express x16 external

graphics interface. Pull low to

disable internal graphics and

enable the x16 interface.

I 3.3V

CMOS

Type 2 only

PCIE_CLK_REF+

PCIE_CLK_REF-

A88

A89

PCIe Reference Clock for all COM

Express PCIe lanes, and for PEG

lanes

O CMOS COM Express only allocates a single

reference clock

2.4.2.

PEG Configuration

The COM Express PCIe Graphics (PEG) Port is comprised of COM Express PCIe lanes 16-31.

The primary use of this set of signals is to interface to off-Module graphics controllers or cards.

The COM Express spec also allows these pins to be shared with a set of Module generated

SDVO lines.

If the PEG interface is not used for an external graphics card or SDVO, it may be possible to use

these PCIe lanes for other Carrier Board PCIe devices. The details of this usage are Module and

Module chip-set dependent. Operation in a x1 link is also supported. Wider links (x2, x4, x8,

x16) are chip-set dependent. Refer to the Module product documentation for details.

The COM Express specification defines a fill order for this set of PCIe lanes. Larger link widths

go to the lower lanes. Refer to the COM Express specification for details.

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

49/218