Reference schematics, Resource allocation, Signal pin# description i/o comment – Kontron COMe Starterkit Eval T2 User Manual

Page 148

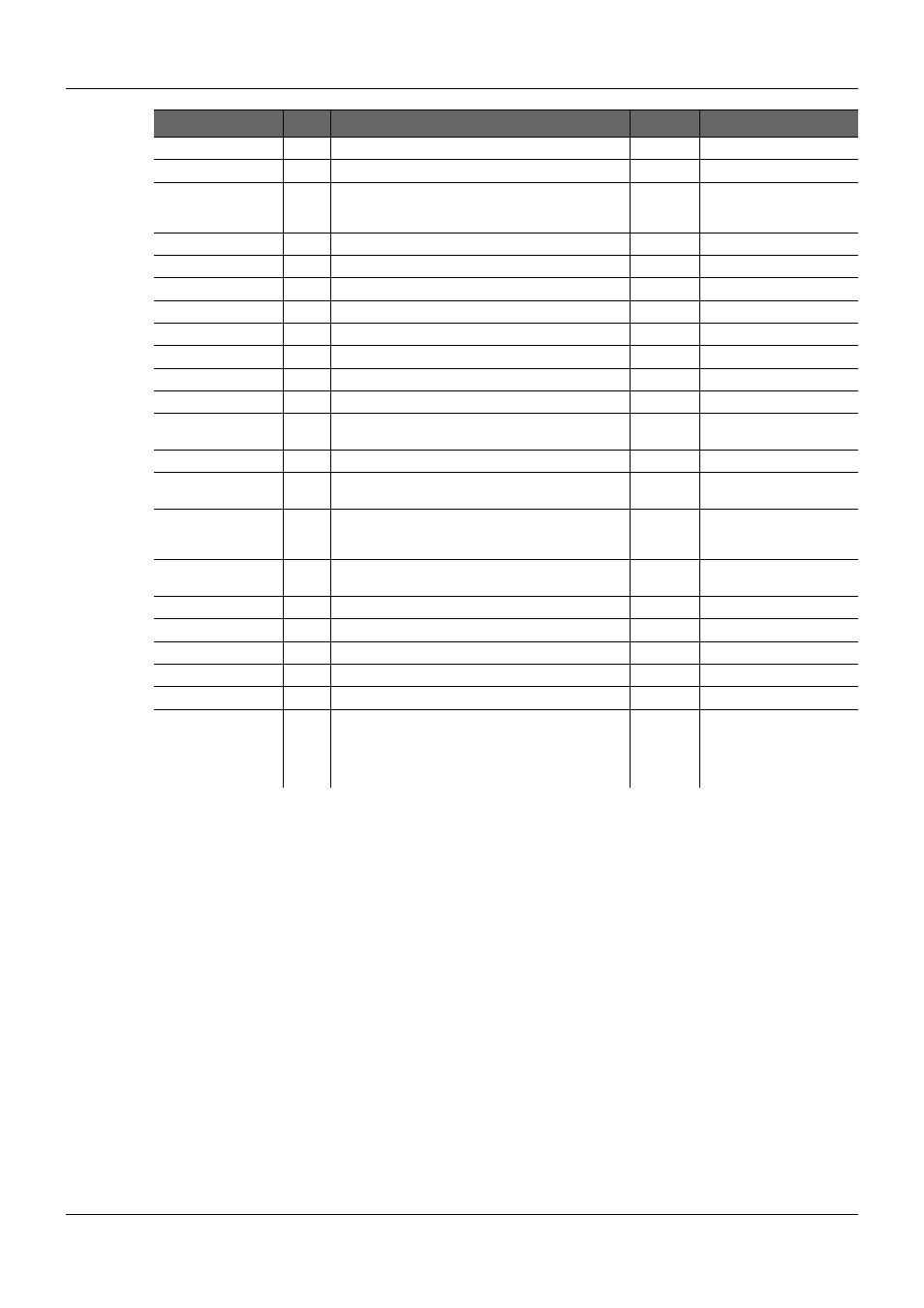

COM Express Interfaces

Signal

Pin# Description

I/O

Comment

PCI_STOP#

D34

PCI bus STOP control line, active low

I/O 3.3V

PCI_PAR

D32

PCI bus parity

I/O 3.3V

PCI_PERR#

C34

Parity Error: An external PCI device drivers PERR#

by driving it low, when it receives data that has a

parity error.

I/O 3.3V

PCI_REQ0#

C22

PCI bus master request input line, active low

I 3.3V

PCI_REQ1#

C19

PCI bus master request input line, active low

I 3.3V

PCI_REQ2#

C17

PCI bus master request input line, active low

I 3.3V

PCI_REQ3#

D20

PCI bus master request input line, active low

I 3.3V

PCI_GNT0#

C20

PCI bus master grant output line, active low

O 3.3V

PCI_GNT1#

C18

PCI bus master grant output line, active low

O 3.3V

PCI_GNT2#

C16

PCI bus master grant output line, active low

O 3.3V

PCI_GNT3#

D19

PCI bus master grant output line, active low

O 3.3V

PCI_RESET#

C23

PCI Reset output, active low

O

3.3V_SBY

Asserted during system

reset

PCI_LOCK#

C35

PCI Lock control line, active low

I/O 3.3V

PCI_SERR#

D33

System Error: SERR# may be pulsed active by any

PCI device that detects a system error condition

I/O 3.3V

PCI_PME#

C15

PCI Power Management Event:

PCI peripherals drive PME# to low to wake up the

system from low-power states S1-S5

I

3V3_SBY

PCI_CLKRUN#

D48

Bidirectional pin used to support PCI clock run

protocol for mobile systems.

I/O 3.3V

PCI_IRQA#

C49

PCI interrupt request line A

I 3.3V

PCI_IRQB#

C50

PCI interrupt request line B

I 3.3V

PCI_IRQC#

D46

PCI interrupt request line C

I 3.3V

PCI_IRQD#

D47

PCI interrupt request line D

I 3.3V

PCI_CLK

D50

PCI 33MHz clock output

O 3.3V

PCI_M66EN

D49

Module input signal that indicates whether a Carrier

Board PCI device is capable of 66MHz operation. It

is pulled to ground by Carrier Board device or by slot

card, if one of the devices is NOT capable of 66MHz

operation.

I 3.3V

2.23.2.

Reference Schematics

2.23.2.1.

Resource Allocation

The COM Express PCI interface is compliant to the 'PCI Local Bus Specification Revision 2.3'. It

supports up to four bus master capable PCI bus slots or external PCI devices designed on the

COM Express Carrier Board. The PCI interface is specified to be +5V tolerant, with +3.3V

signaling. All necessary PCI bus pull-up resistors must be included on the COM Express

Module.

Allocate PCI resources (IDSEL pin assignments, interrupts, request lines and grant lines) per

Figure 59: PCI Bus Interrupt Routing below. The PCI Specification requires that PCI devices be

capable of sharing interrupts. Interrupt latency is reduced if devices do not share interrupts;

hence the interrupt “rotation” scheme shown below is recommended. If there are more than four

PCI devices in the system, then some interrupt-sharing is inevitable.

The signal 'IDSEL' of each external PCI device or PCI slot has to be connected through a 22Ω

resistor to a separate PCI address line. For PCI bus slots 1-4, COM Express specifies the PCI

address lines AD[20] to AD[23].

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

148/218