Hapter, Configuring the speed/voltage loop, Figure 5.1 – speed loop block diagram – Rockwell Automation FlexPak 3000 Digital DC Drive Version 4.3 User Manual

Page 49

Configuring the Speed/Voltage Loop

5-1

C

HAPTER

5

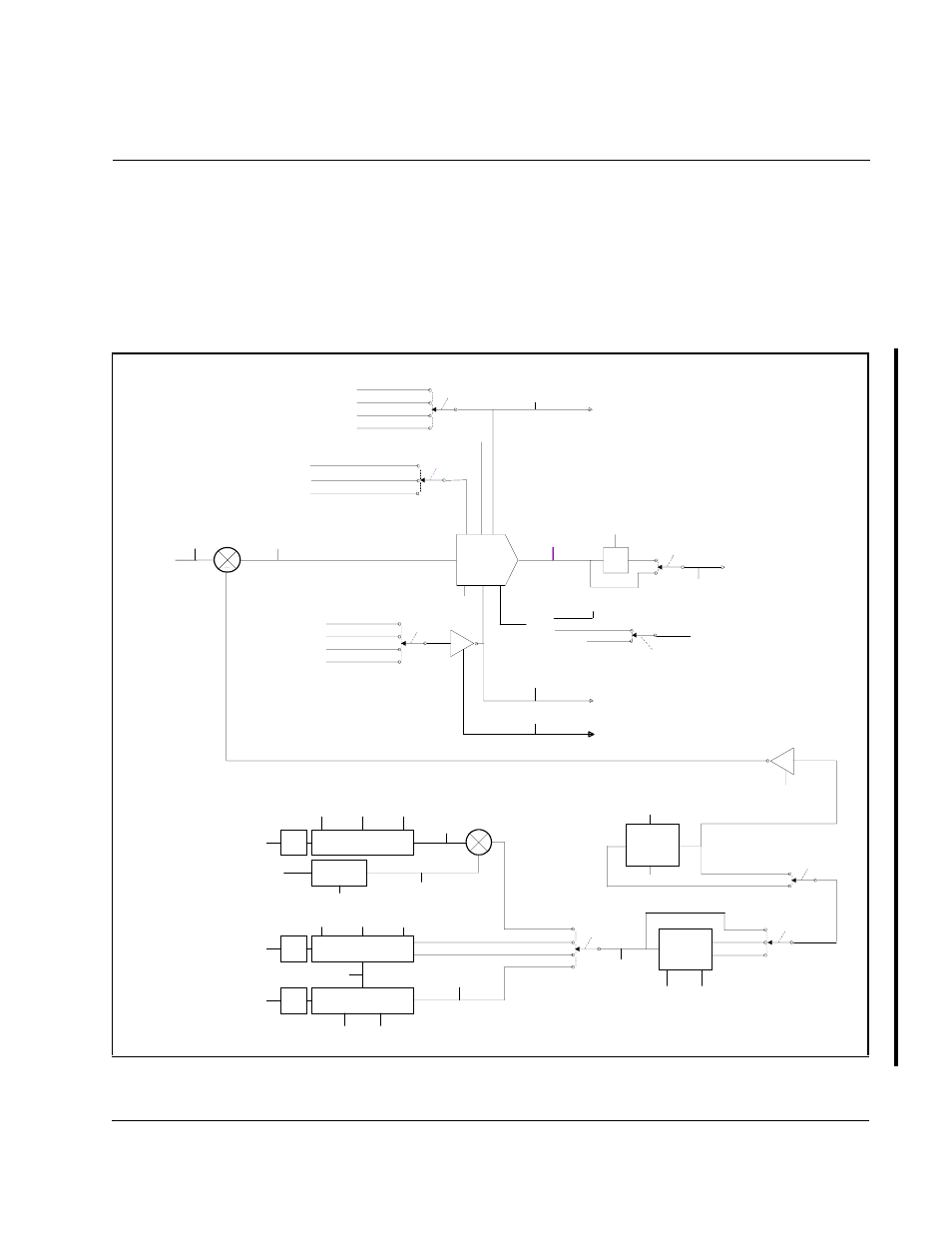

Configuring the Speed/Voltage Loop

This chapter describes configuring the speed/voltage loop functions. These include

jog, lead/lag, speed loop lag, current limits, the speed loop

PI

block, and winding.

The full speed loop block diagram, including these features, is shown in figure 5.1.

Figure 5.1 – Speed Loop Block Diagram

SPD LOOP

LAG FREQ

SPD LOOP PI

PROP GAIN

(SPD LOOP

OUTPUT)

SPD LOOP

LAG BYPASS

OFF

*ON

(SPD LOOP ERROR)

WLG

La

g

(SPD LOOP

LAG OUTPUT)

SPD LOOP PI

LEAD FREQ

PI

KP HI

WLD

RST

NEGATIVE CURRENT LIM

ANALOG IN 2

NETW IN REG 1, 2, 3

From Network

From I/O Expansion Board

Inputs Block Diagram

{

NEG CURRENT

LIM SEL

*REGISTER

ANALOG IN 1

+

INV

EN

NEG CUR LIM

INV EN

POSITIVE CURRENT LIM

*REGISTER

ANALOG IN 1

ANALOG IN 2

NETW IN REG 1, 2, 3

From Network

From I/O Expansion Board

Inputs Block Diagram

{

SPD LOOP CUR LIM

POS CURRENT

LIM SEL

SPD LOOP

PI LIMITS

INIT

LO

OR

Internal Sequencing

(Drive Stopped)

Off

(Other)

NETWORK

CONTROL SOURCE

SELECT

SPD LOOP PI

RESET (Network)

0

*ZERO

SPD LOOP PI INIT VAL

ANALOG MANUAL TRIM REF

ANALOG MANUAL TRIM REF

From Network

SPD LOOP

PI INIT SEL

(CML FEEDBACK)

8 sample average

Analog Tachometer

(+ hi) terminal 21

(+ lo) terminal 22

(–) terminal 23

Pulse Encoder

(from optional

Pulse Encoder kit)

EN

UNDERWIND

ENABLE

*ARMATURE VOLT

DC TACH

AC TACH

PULSE TACH

FEEDBACK

SELECT

(ANALOG TACH FEEDBACK)

(PULSE TACH

FEEDBACK)

SPD LEADLAG

LOW FREQ

SPD LEADLAG

RATIO

*BYPASS

LEAD/LAG

LAG/LEAD

SPD LEADLAG

SELECT

Lead/Lag

or

Lag/Lead

WLD

WRATIO

+

–

Armature

Voltage

(internal)

MOTOR RATED

ARM VOLTS

ARM VOLTAGE

GAIN ADJ

ARM VOLTAGE

ZERO ADJ

(ARMATURE

VOLTAGE)

Software Scaling

A/D

Software

Scaling

IR COMPENSATION

(IR COMPENSATION TP)

ANALOG TACH

ZERO ADJ

ANALOG TACH

GAIN ADJ

ANLG TACH

VOLTS/1000

Software Scaling

A/D

TOP SPEED

Software Scaling

F/D

PULSE TACH PPR

PULSE TACH

QUADRATURE

KEYPAD, TERMBLK,

or SERIAL

NETWORK

CONTROL

SOURCE

SELECT

DIV

IN

OUT

1000

SPEED FEEDBACK GAIN

Gain

MUL

(SPD LOOP

FEEDBACK)

(SPD LOOP

REFERENCE

To figure 6.1, Current

Minor Loop Reference

Path Block Diagram

From figure 4.7,

Speed Reference

Mode Select Block

Diagram

To figure 6.1, Current

Minor Loop Reference

Path Block Diagram