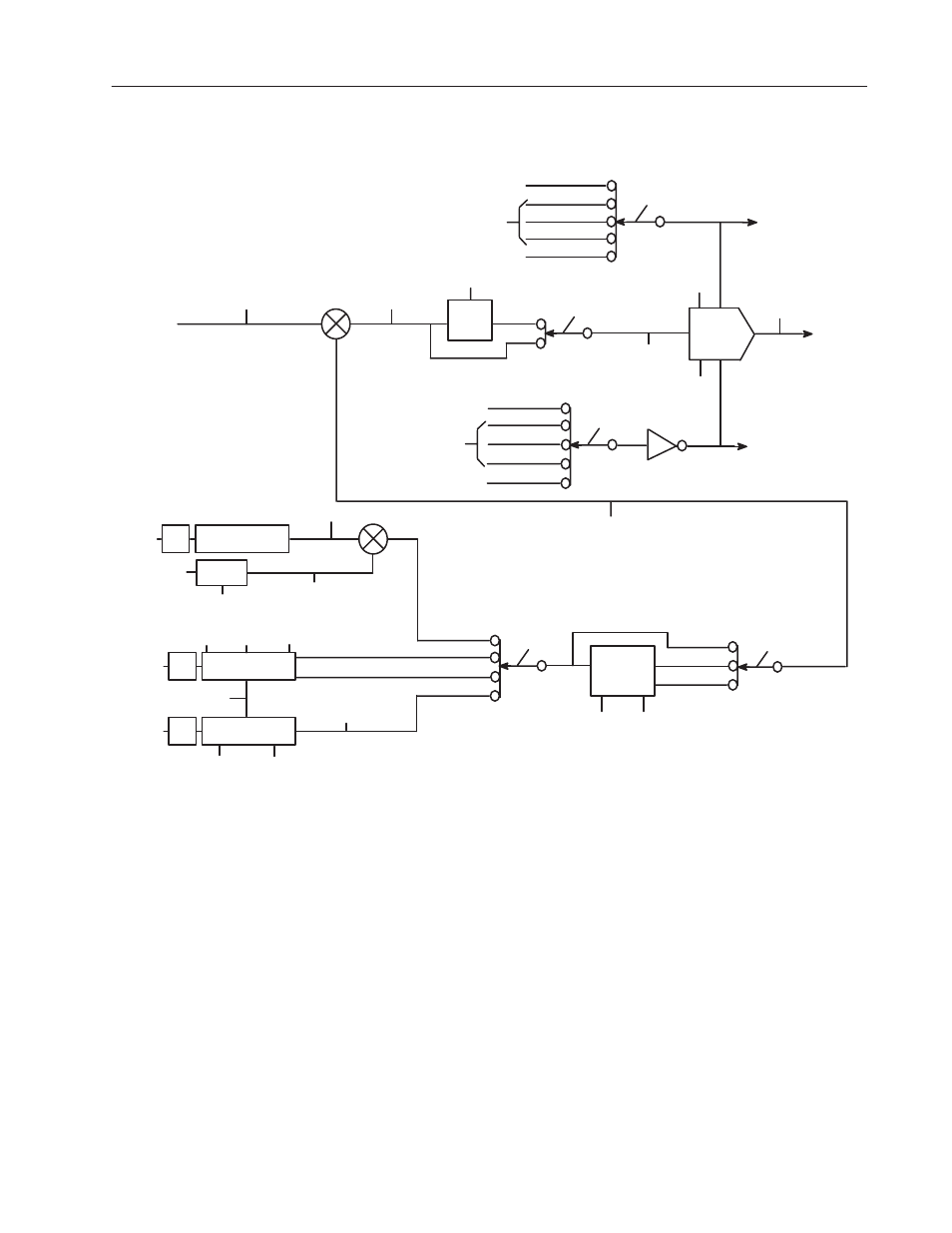

Figure a.7 speed loop, Firmware block diagrams a–7 – Rockwell Automation 1397 DC Drive Firmware 2.xx User Manual

Page 225

Firmware Block Diagrams

A–7

Publication 1397-5.0 — June, 2001

Figure A.7

Speed Loop

Spd Loop Fdbk

(P. 022)

–

+

WLG

ADAPTOR 1–6

*ON

Spd Lp Lag Type

(P. 076)

OFF

LAG

Max Motor Speed

(P. 041)

LEAD/LAG

FREQUENCY IN

KP

Spd Loop Output

(P. 024)

*BYPASS

Pos Current Lim

(P. 067)

ANALOG IN 3

*REGISTER

From I/O

Exp. Inputs

Block Diagram

SOFTWARE SCALING

Pos Cur

Lim Src

(P. 069)

Spd Loop Ref

(P. 025)

From Speed

Reference

Mode Select

Block Diagram

ANALOG IN 4

FREQUENCY IN

ADAPTOR 1–6

To CML

Reference

Block Diagram

HI

To CML

Reference

Block Diagram

PI

WLD LO

Neg Cur

Lim Src

(P. 070)

ANALOG IN 3

*REGISTER

Neg Cur Lim

(P. 068)

ANALOG IN 4

To CML

Reference

Block Diagram

From I/O

Exp Inputs

Block Diagram

From SCANport

LAG/LEAD

LEAD/LAG

or

LAG/LEAD

(SPD

LEAD/LAG

FREQ)

(SPD

LEAD/LAG

RATIO)

–

+

Feedback Type

(P. 039)

PULSE TACH

DC TACH

*ARM VOLT

AC TACH

Arm Voltage (P. 004)

From SCANport

A/D

SOFTWARE

SCALING

Armature

Voltage

Internal

(CUR LOOP FDBK)

8 sample average

IR Compensation (P. 066)

IR Comp TP (P.179)

SOFTWARE SCALING

A/D

F/D

SOFTWARE SCALING

Encoder Quad

(P. 049)

Encoder

PPR

(P. 048)

Encoder Fdbk

(P. 189)

Anlg Tach

Zero

(P. 058)

Anlg Tach

Gain

(P. 057)

Anlg Tach

V/1000

(P. 047)

ANLG TACH

(+ hi) CTB–21

(+ lo) CTB–22

( – ) CTB

Pulse

Tachometer

(From optional

pulse tach kit)

*Default Selection

Spd Lag Freq

(P. 075)

Spd Loop Lag Out

(P. 023)

Spd Loop Kp

(P. 078)

Spd Lp

Lead Freq

(P. 077)

Spd Loop Error

(P. 021)

(ANLG TACH FDBK)

Spd Lead/Lag Type

(P. 074)