Figure 9-8. receive done-queue structure – Rainbow Electronics DS31256 User Manual

Page 99

DS31256

99 of 181

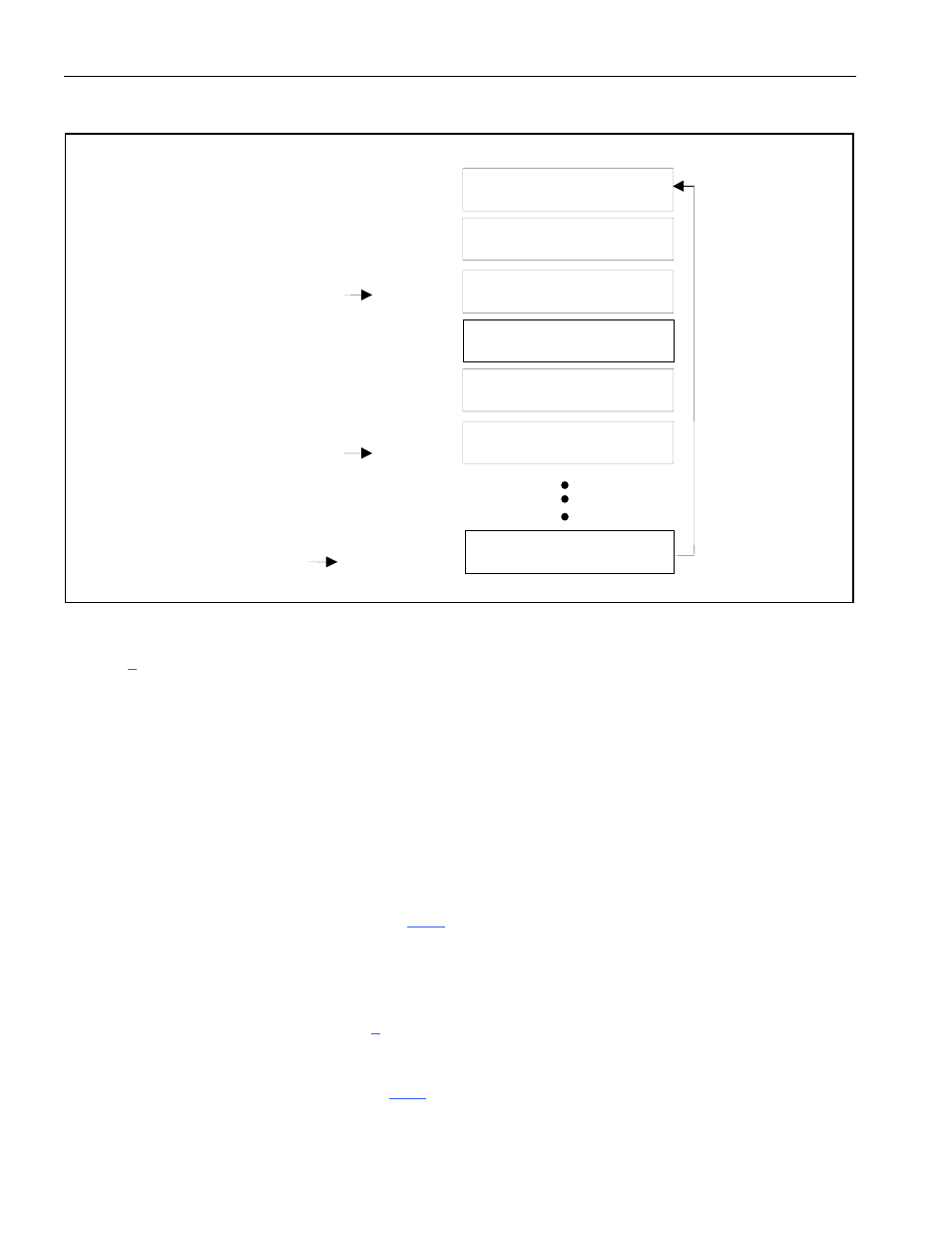

Figure 9-8. Receive Done-Queue Structure

Once the receive DMA is activated (through the RDE control bit in the master configuration register, see

Section

), it can begin writing data to the done queue. It knows where to write data into the done queue

by reading the write pointer and adding it to the base address to obtain the actual 32-bit address. Once

the DMA has written to the done queue, it increments the write pointer by one dword. A check must be

made to ensure the incremented address does not exceed the receive done queue end address. If the

incremented address exceeds this address, the incremented write pointer is set equal to 0000h (i.e., the

base address).

Status Bits/Interrupts

On writes to the done queue by the DMA, the DMA sets the status bit for the receive DMA done-queue

write (RDQW) in the SDMA. The host can configure the DMA to either set this status bit on each write

to the done queue or only after multiple (from 2 to 128) writes. The host controls this by setting the

RDQT0 to RDQT2 bits in the receive DMA queues control (RDMAQ) register. See the description of

the RDMAQ register at the end of Section

for more details. The DMA also checks the receive

done-queue host read pointer to ensure an overflow does not occur. If this does occur, the DMA then sets

the status bit for the receive DMA done-queue write error (RDQWE) in the status register for DMA

(SDMA), and it does not write to the done queue nor does it increment the write pointer. In such a

scenario, packets can be lost and unrecoverable. Each of the status bits can also (if enabled) cause a

hardware interrupt to occur. See Section

for more details.

Buffer Write Threshold Setting

In the DMA configuration RAM (Section

), there is a host-controlled field called “threshold” (bits

RDT0 to RDT2) that informs the DMA when it should write to the done queue. The host has the option

to have the DMA place information in the done queue after a programmable number (from 1 to 7) data

Base + 00h

Base + 04h

Base + 08h

Base + 0Ch

Base + 10h

Base + 14h

Base + End Address

Done-Queue DMA Write Pointer

Done-Queue Host Read Pointer

Maximum of 65,536

Done-Queue Descriptors

DMA Readied

Done-Queue Descriptor

DMA Readied

Done-Queue Descriptor

DMA Readied

Done-Queue Descriptor

DMA Readied

Done-Queue Descriptor

Host Processed

Done-Queue Descriptor

Host Processed

Done-Queue Descriptor

Host Processed

Done-Queue Descriptor