Figure 11-12. 8-bit write cycle – Rainbow Electronics DS31256 User Manual

Page 162

DS31256

162 of 181

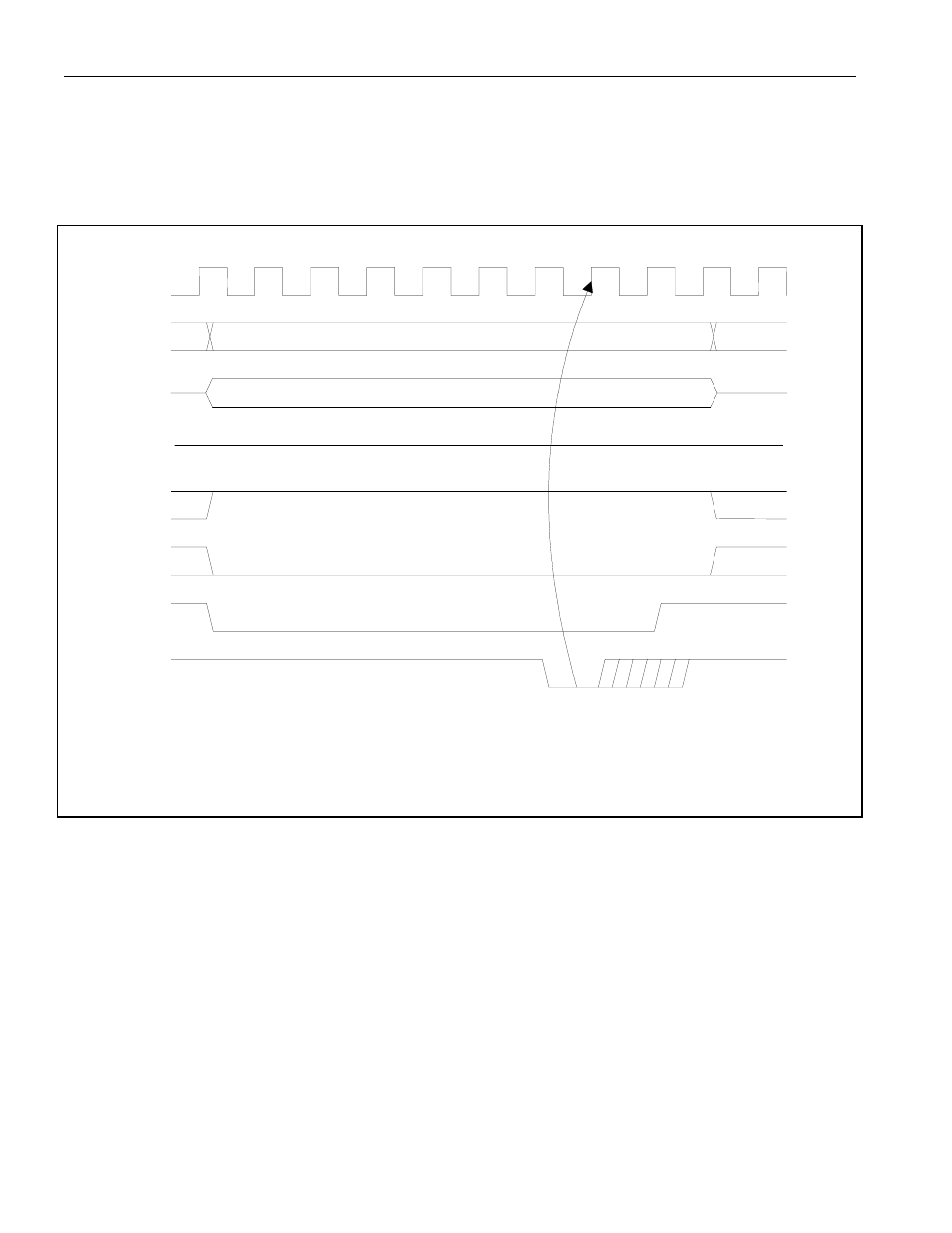

Figure 11-12. 8-Bit Write Cycle

Motorola Mode (LIM = 1)

Arbitration Disabled (LARBE = 0)

Bus Transaction Time = Timed from LRDY (LRDY = 0000)

LCLK

LA[19:0]

LD[7:0]

LD[15:8]

LR/

W

LDS

Address Valid

LBHE

LRDY

Three-State

Data Valid

1

2

3

4

5

6

7

8

9

10

Note: The

LRDY signal must be detected by the 9th LCLK or the bus access attempted by the host is unsuccessful and the LBE status

bit is set.

See also other documents in the category Rainbow Electronics Communication:

- MAX12005 (14 pages)

- MAX7058 (14 pages)

- MAX9995 (13 pages)

- MAX7034 (13 pages)

- MAX7033 (16 pages)

- MAX9476 (8 pages)

- MAX9486 (8 pages)

- MAX14821 (29 pages)

- MAX9489 (11 pages)

- MAX9491 (11 pages)

- DS2130Q (22 pages)

- DS21458 (270 pages)

- DS3131 (174 pages)

- DS26502 (125 pages)

- DS2153Q (48 pages)

- DS26503 (123 pages)

- DS2186 (11 pages)

- DS1842A (6 pages)

- DS3134 (203 pages)

- DS1876 (69 pages)

- DS1874 (88 pages)

- DS2141A (35 pages)

- DS3184 (13 pages)

- DS2154 (69 pages)

- DS26504 (128 pages)

- DS3164 (12 pages)

- DS1852 (25 pages)

- DS2181A (32 pages)

- DS2151Q (46 pages)

- DS1843 (8 pages)

- DS2165Q (17 pages)

- DS3170 (233 pages)

- DS2180A (36 pages)

- DS2172 (20 pages)

- DS2152 (79 pages)

- DS1841 (16 pages)

- DS2182A (22 pages)

- DS2143Q (40 pages)

- DS2132A_Q (17 pages)

- DS1862 (42 pages)

- DS26519 (310 pages)

- DS2188 (11 pages)

- DS1875 (92 pages)

- DS33M33 (20 pages)