Transmit side, Overview, Ransmit – Rainbow Electronics DS31256 User Manual

Page 105: Tion, 3 transmit side, 1 overview

DS31256

105 of 181

ready to be read. During a write operation, this bit is set to 1 while the write is taking place. It is set to 0 once the

write operation has completed.

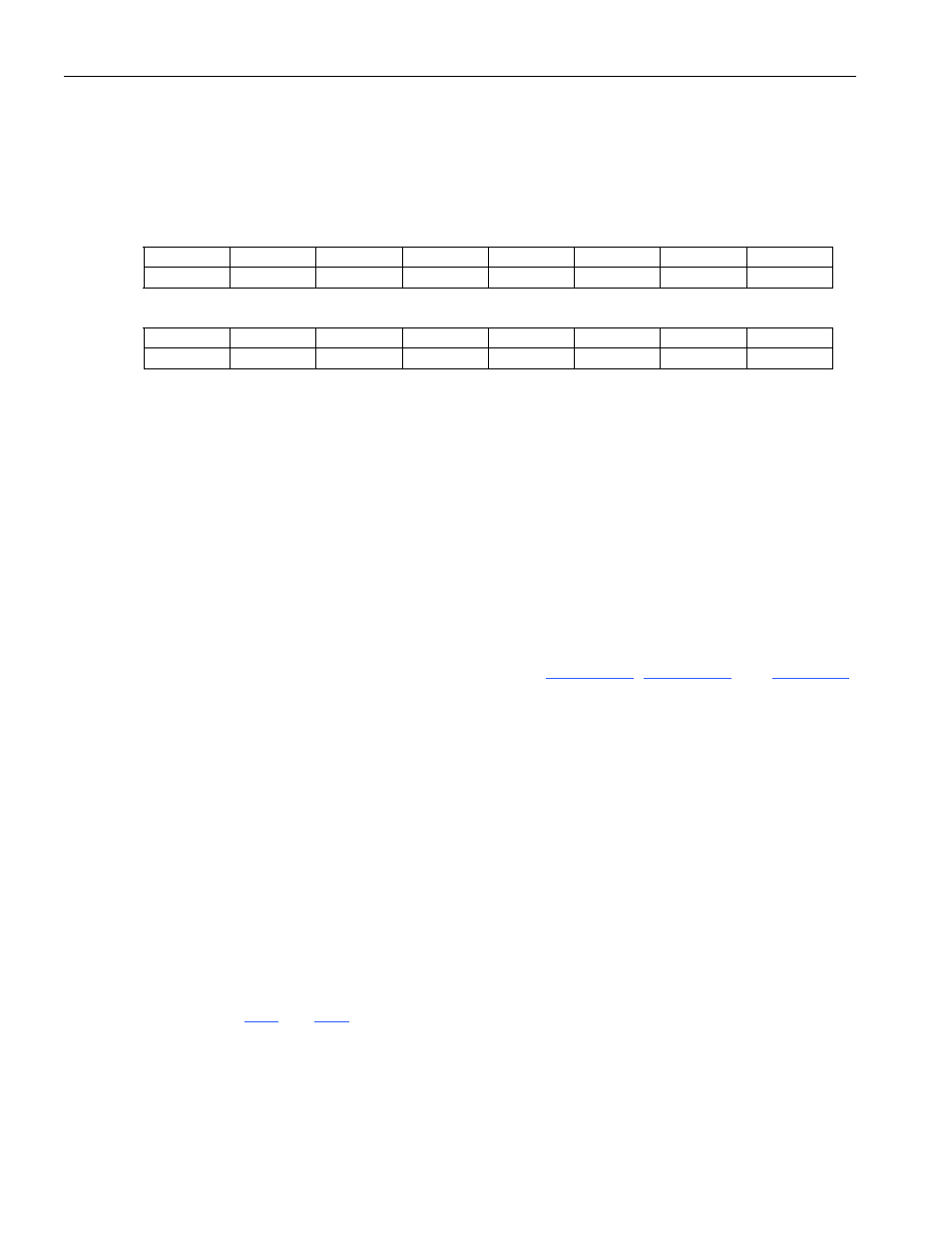

Register Name:

RDMAC

Register Description: Receive DMA Channel Configuration

Register Address:

0774h

Bit

# 7 6 5 4 3 2 1 0

Name D7 D6 D5 D4 D3 D2 D1 D0

Default

Bit

# 15 14 13 12 11 10 9 8

Name D15 D14 D13 D12 D11 D10 D9 D8

Default

Note: Bits that are underlined are read-only, all other bits are read-write.

Bits 0 to 15/Receive DMA Configuration RAM Data (D0 to D15). Data that is written to or read from the

receive DMA configuration RAM.

9.3 Transmit Side

9.3.1 Overview

The transmit DMA uses a scatter-gather technique to read packet data from main memory. The host

keeps track of and decides from where (and when) the DMA should grab the outgoing packet data. A set

of descriptors that get handed back and forth between the host and the DMA can tell the DMA where to

obtain the packet data, and the DMA can tell the host when the data has been transmitted.

The transmit DMA operation has three main areas, as shown in

, and

The host writes to the pending queue, informing the DMA which channels have packet data ready to be

transmitted. Associated with each pending-queue descriptor is a data buffer that contains the actual data

payload of the HDLC packet. The data buffers can be between 1 and 8188 Bytes in length (inclusive). If

an outgoing packet requires more memory than a data buffer contains, the host can link the data buffers

to handle packets of any size.

The done-queue descriptors contain information that the DMA wishes to pass to the host. The DMA

writes to the done queue when it has completed transmitting either a complete packet or data buffer (see

below for the discussion on the DMA update to the done queue). Through the done-queue descriptors,

the DMA informs the host about the status of the outgoing packet data. If an error occurs in the

transmission, the done queue can be used by the host to recover the packet data that did not get

transmitted and the host can then re-queue the packets for transmission.

If enabled, the DMA can burst read the pending-queue descriptors and burst write the done-queue

descriptors. This helps minimize PCI bus accesses, freeing the PCI bus up to do more time-critical

functions. See Sections

for more details on this feature.