Figure 9-16. transmit packet descriptors – Rainbow Electronics DS31256 User Manual

Page 115

DS31256

115 of 181

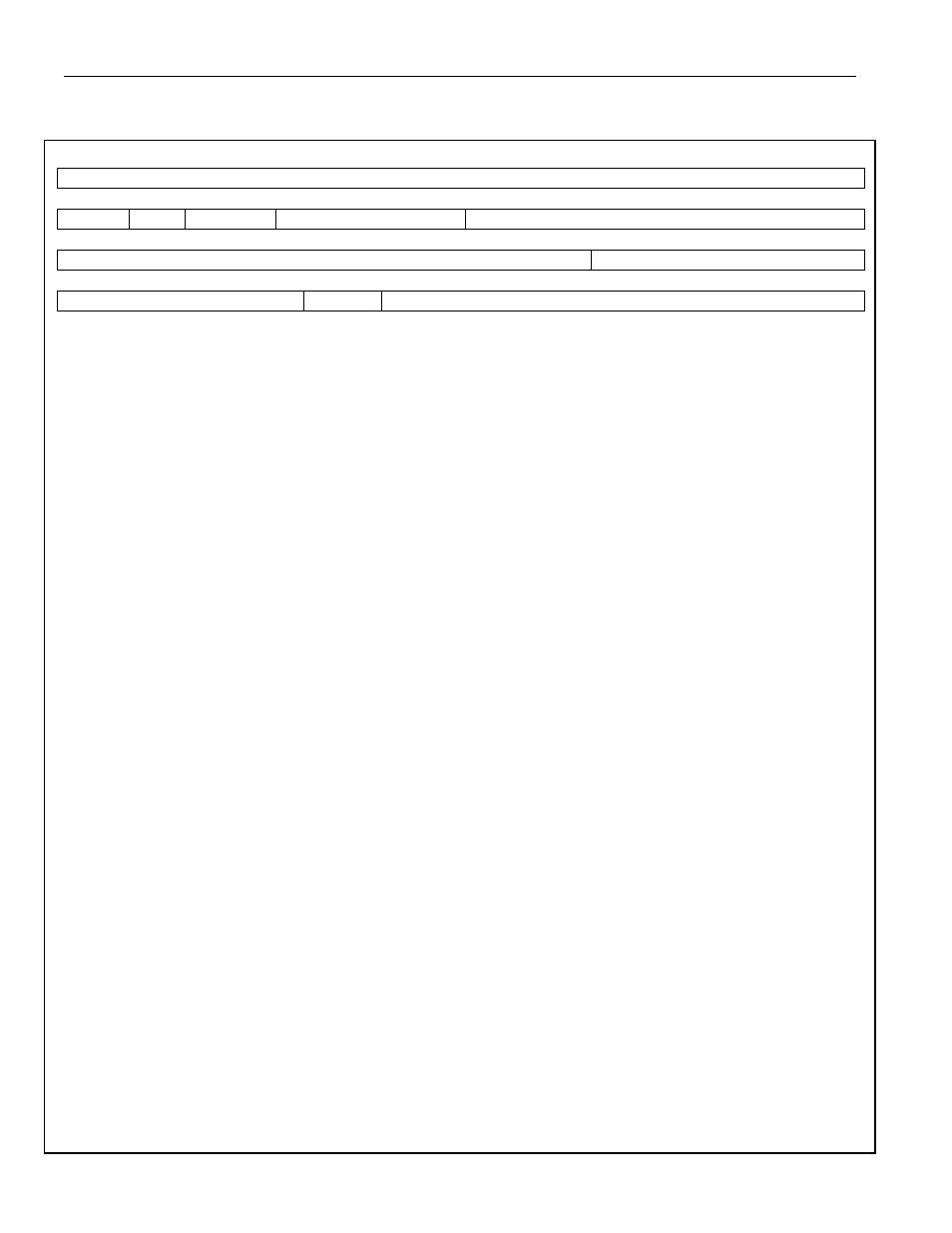

Figure 9-16. Transmit Packet Descriptors

dword 0

Data Buffer Address (32)

dword 1

EOF

CV

unused

Byte Count (13)

Next Descriptor Pointer (16)

dword 2

unused (24)

HDLC CH# (8)

dword 3

unused (15)

PV

Next Pending Descriptor Pointer (16)

Note 1: The organization of the transmit descriptor is not affected by the enabling of Big Endian.

Note 2: The format of the transmit descriptor is almost identical to the receive descriptor; this lessens the burden of the host in preparing

descriptors in store-and-forward applications.

Note 3: Next descriptor pointer is an index, not an absolute address.

dword 0; Bits 0 to 31/Data Buffer Address. Direct 32-bit starting address of the data buffer that is associated

with this transmit descriptor.

dword 1; Bits 0 to 15/Next Descriptor Pointer. This 16-bit value is the offset from the transmit descriptor base

address of the next descriptor in the chain. Only valid if EOF = 0 (next descriptor in the same packet chain) or if

EOF = 1 and CV = 1 (first descriptor in the next packet).

dword 1; Bits 16 to 28/Byte Count. Number of bytes stored in the data buffer. Maximum is 8188 Bytes (0000h =

0 Bytes / 1FFCh = 8188 Bytes).

dword 1; Bit 29/Unused. This bit is ignored by the transmit DMA and can be set to any value.

dword 1; Bit 30/Chain Valid (CV). If CV is set to 1 when EOF = 1, then this indicates that the next descriptor

pointer field is valid and corresponds to the first descriptor of the next packet that is queued up for transmission.

The CV bit is ignored when EOF = 0.

dword 1; Bit 31/End of Frame (EOF). When set to 1, this bit indicates that the descriptor is the last buffer in the

current packet. When set to 0, this bit indicates that next descriptor pointer field is valid and points to the next

descriptor in the packet chain.

dword 2; Bits 0 to 7/HDLC Channel Number. HDLC channel number, which can be from 1 to 256.

00000000 (00h) = HDLC channel number 1

11111111 (FFh) = HDLC channel number 256

dword 2; Bits 8 to 31/Unused. These bits are ignored by the transmit DMA and can be set to any value.

dword 3; Bits 0 to 15/Next Pending Descriptor Pointer. This 16-bit value is the offset from the transmit

descriptor base address to another descriptor chain that is queued up for transmission. The transmit DMA can store

up to two queued packet chains internally, but additional packet chains must be stored as a link list by the transmit

DMA using this field. This field is only valid if PV = 1, and it should be set to 0000h by the host when the host is

preparing the descriptor.

dword 3; Bit 16/Pending Descriptor Valid (PV). If set, this bit indicates that the next pending descriptor pointer

field is valid and corresponds to the first descriptor of the next packet chain that is queued up for transmission.

This field is written to by the transmit DMA to link descriptors together and should always be set to 0 by the host.

dword 3; Bits 17 to 31/Unused. These bits are ignored by the transmit DMA and can be set to any value.