Pending queue, Figure 9-17. transmit pending-queue descriptor, 3 pending queue – Rainbow Electronics DS31256 User Manual

Page 116

DS31256

116 of 181

9.3.3 Pending Queue

The host writes to the transmit pending queue the location of the readied descriptor, channel number, and

control information. The descriptor space is indicated through a 16-bit pointer, which the DMA uses

with the transmit packet-descriptor base address to find the exact 32-bit address of the associated

transmit packet descriptor.

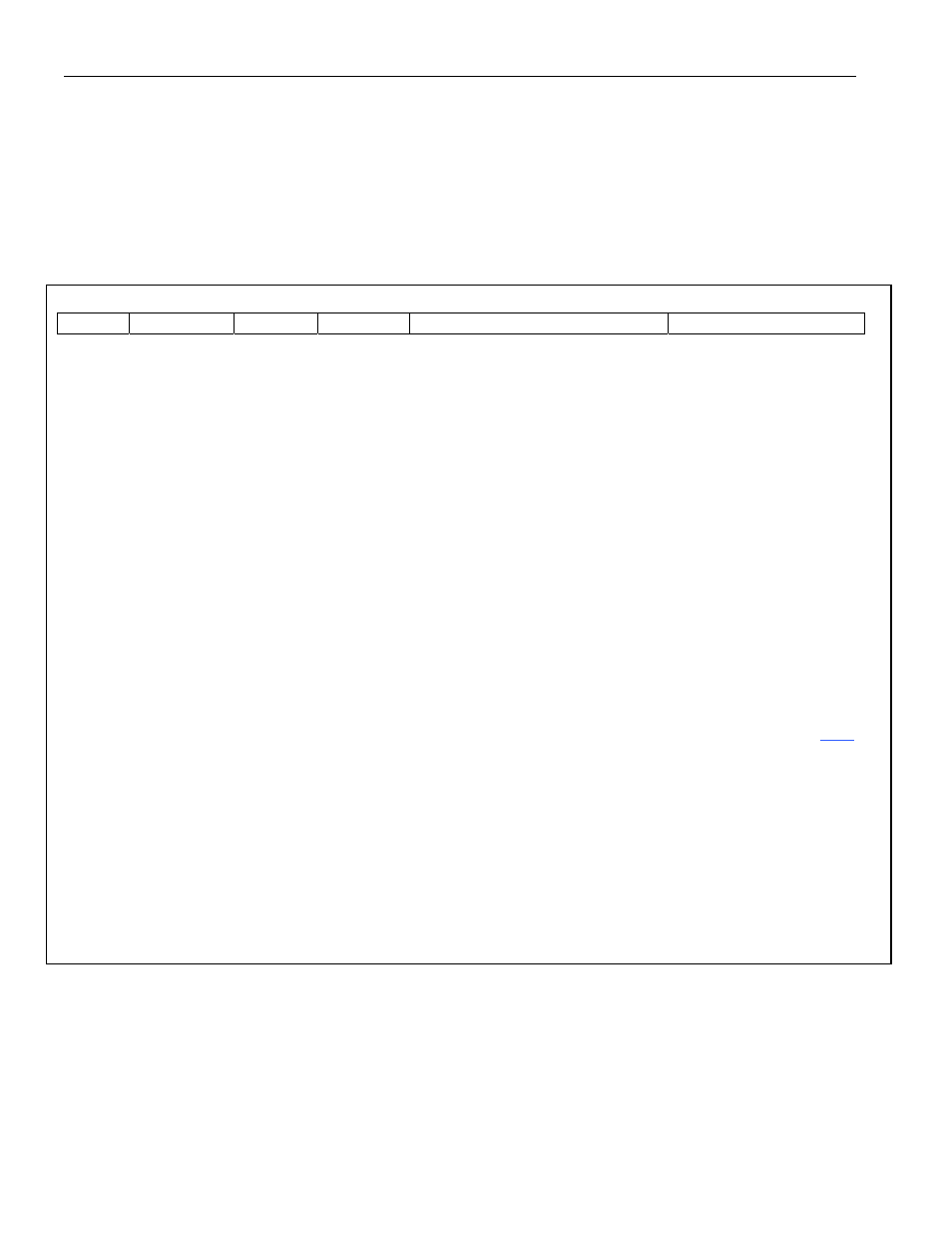

Figure 9-17. Transmit Pending-Queue Descriptor

dword 0

unused

Status(3)

CH RST

PRI

HDLC CH#(8) Descriptor

Pointer

(16)

Note 1: The organization of the pending queue is not affected by the enabling of Big Endian.

Note 2: Decriptor pointer is an index, not an absolute address.

dword 0; Bits 0 to 15/Descriptor Pointer. This 16-bit value is the offset from the transmit descriptor base

address to the first descriptor in a packet chain (can be a single descriptor) that is queued up for transmission.

dword 0; Bits 16 to 21/HDLC Channel Number. HDLC channel number, which can be from 1 to 40.

00000000 (00h) = HDLC channel number 1

11111111 (FFh) = HDLC channel number 256

dword 0; Bit 24/Priority Packet (PRI). If this bit is set to 1, this indicates to the transmit DMA that the packet or

packet chain pointed to by the descriptor pointer field should be transmitted immediately after the current packet

transmission (whether it be standard or priority) is complete.

dword 0; Bit 25/Channel Reset (CHRST). Under normal operating conditions, this bit should always be set to 0.

When an error condition occurs and the transmit DMA places the channel into an out-of-service state by setting

the channel enable (CHEN) bit in the transmit DMA configuration register to 0, the host can force the channel

active again by setting the CHRST bit to 1. Only the first descriptor loaded into the pending queue after an error

condition should have CHRST set to 1; all subsequent descriptors (until another error condition occurs) should

have CHRST set to 0. The transmit DMA examines this bit and forces the channel active (CHEN = 1) if CHRST is

set to 1. If CHRST is set to 0, then the transmit DMA does not modify the state of the CHEN bit. See Section

for more details about how error conditions are handled.

dword 0; Bits 26 to 28/Packet Status. Not used by the DMA. Can be set to any value by the host and is ignored

by the transmit DMA. This field is used by the transmit DMA when it writes to the done queue to inform the host

of the status of the outgoing packet data.

dword 0; Bits 29 to 31/Unused. Not used by the DMA. Can be set to any value by the host and is ignored by the

transmit DMA.