Table 2-a. restrictions for rev b1/b2 silicon – Rainbow Electronics DS31256 User Manual

Page 11

DS31256

11 of 181

Restrictions

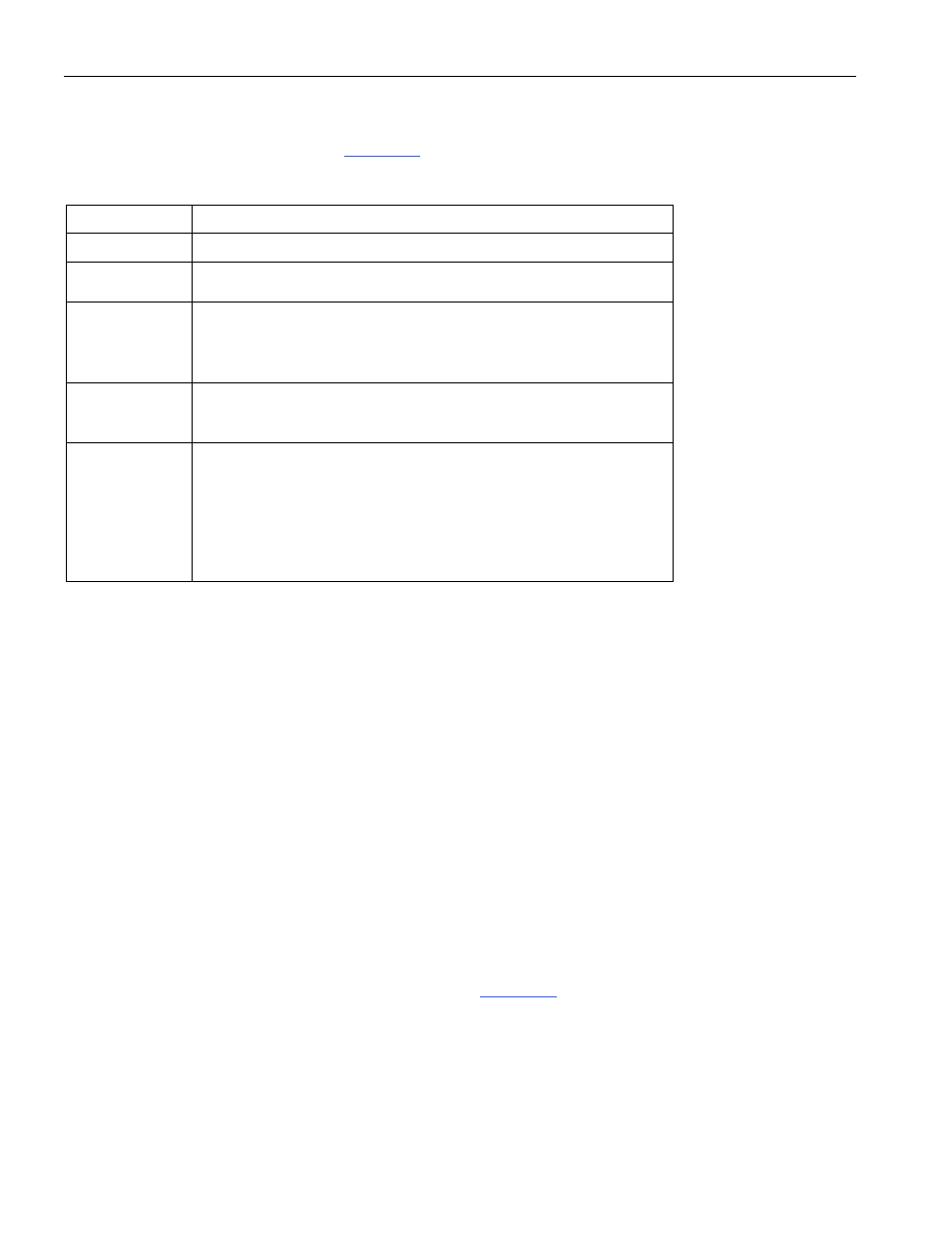

In creating the overall system architecture, the user must balance the port, throughput, and HDLC

channel restrictions of the DS31256.

lists all of the upper-bound maximum restrictions.

Table 2-A. Restrictions for Rev B1/B2 Silicon

ITEM RESTRICTION

Port

Maximum of 16 channelized and unchannelized physical ports

Unchannelized

Ports 0 to 2: Maximum data rate of 52Mbps

Ports 3 to 15: Maximum data rate of 10 Mbps

Channelized and with frame interleave interfaces or a minimum of

two/multiple of two consecutive DS0 time slots assigned to one

HDLC channel: 64 T1/E1 channels

Channelized

Channelized and with byte interleave interfaces: 64 T1/E1 channels

Maximum receive: 132Mbps

Throughput

Maximum transmit: 132Mbps

HDLC

Maximum of 256 channels:

If the fast HDLC engine on Port 0 is being used, then it must be

HDLC Channel 1*

If the fast HDLC engine on Port 1 is being used, then it must be

HDLC Channel 2*

If the fast HDLC engine on Port 2 is being used, then it must be

HDLC Channel 3*

*The 256 HDLC channels within the device are numbered 1 to 256.

Internal Device Configuration Registers

All internal device configuration registers (with the exception of the PCI configuration registers, which

are 32-bit registers) are 16 bits wide and are not byte addressable. When the host on the PCI bus accesses

these registers, the particular combination of byte enables (i.e., PCBE signals) is not important, but at

least one of the byte enables must be asserted for a transaction to occur. All registers are read/write,

unless otherwise noted. Not assigned (n/a) bits should be set to 0 when written to allow for future

upgrades. These bits should be treated as having no meaning and could be either 0 or 1 when read.

Initialization

On a system reset (which can be invoked by either hardware action through the PRST signal or software

action through the RST control bit in the master reset and ID register), all of the internal device

configuration registers are set to 0 (0000h). The local bus bridge mode control register (LBBMC) is not

affected by a software-invoked system reset; it is forced to all zeros only by a hardware reset. The

internal registers that are accessed indirectly (these are listed as “indirect registers” in the data sheet and

consist of the channelized port registers in the Layer 1 block, the DMA configuration RAMs, the HDLC

configuration registers, and the FIFO registers) are not affected by a system reset, so they must be

configured on power-up by the host to a proper state.

lists the steps required to initialize the

DS31256.

Note: After device power-up and reset, it takes 0.625ms to get a port up and operating, therefore, the

ports must wait a minimum of 0.625ms before packet data can be processed.