Figure 9-13. transmit dma priority packet handling – Rainbow Electronics DS31256 User Manual

Page 111

DS31256

111 of 181

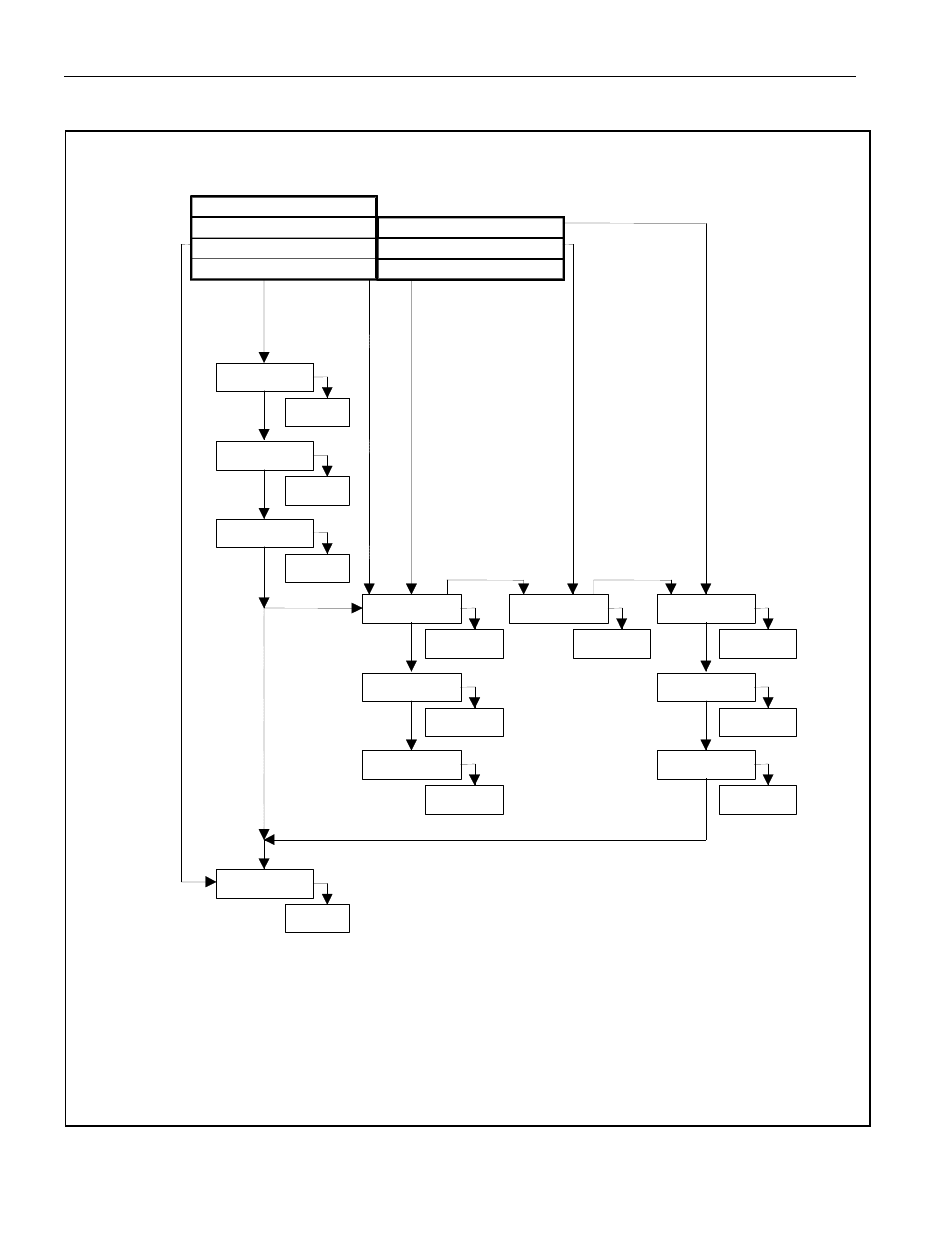

Figure 9-13. Transmit DMA Priority Packet Handling

Buffer 1

Packet 1

1st Descriptor

(EOF=0/CV=0)

Buffer 2

Packet 1

2nd Descriptor

(EOF=0/CV=0)

Buffer 3

Packet 1

Last Descriptor

(EOF=1/CV=1)

Buffer 1

Packet 2

Last Descriptor

(EOF=1/CV=0)

Buffer 1

Pri. Packet 1

1st Descriptor

(EOF=0/CV=0)

Buffer 2

Pri. Packet 1

Last Descriptor

(EOF=1/CV=1)

Buffer 1

Pri. Packet 2

Last Descriptor

(EOF=1/CV=0)

Buffer 1

Pri. Packet 3

Last Descriptor

(EOF=1/CV=0)

Buffer 1

Pri. Packet 4

1st Descriptor

(EOF=0/CV=0)

Buffer 2

Pri. Packet 4

2nd Descriptor

(EOF=0/CV=0)

Buffer 3

Pri. Packet 4

Last Descriptor

(EOF=1/CV=0)

Next Descriptor Pointer

Start Descriptor Pointer

Transmit DMA Configuration RAM

Normal

Path if No

Priority

Packets

Had

Occurred

Service

Priority

Packets

All Priority Packets Have Been Serviced

Next Pending Descriptor Pointer

Last Pending Descriptor Pointer

Next Pending Descriptor Pointer

Next Descriptor Pointer

Last Pending Descriptor Pointer

Standard Queue Pointers

Priority Queue Pointers

Note 1: The start descriptor pointer field in the transmit DMA configuration RAM is used by both the normal and

priority pending queues.

See

Note 1

PV = 1

Next Pending

Descriptor Pointer

stored within the

Packet Descriptor

Standard

Packet Chain

Column 1

Priority

Packet Chain

Column 2

Priority

Packet Chain

Column 3

Priority

Packet Chain

Column 4