Rainbow Electronics DS31256 User Manual

Page 72

DS31256

72 of 181

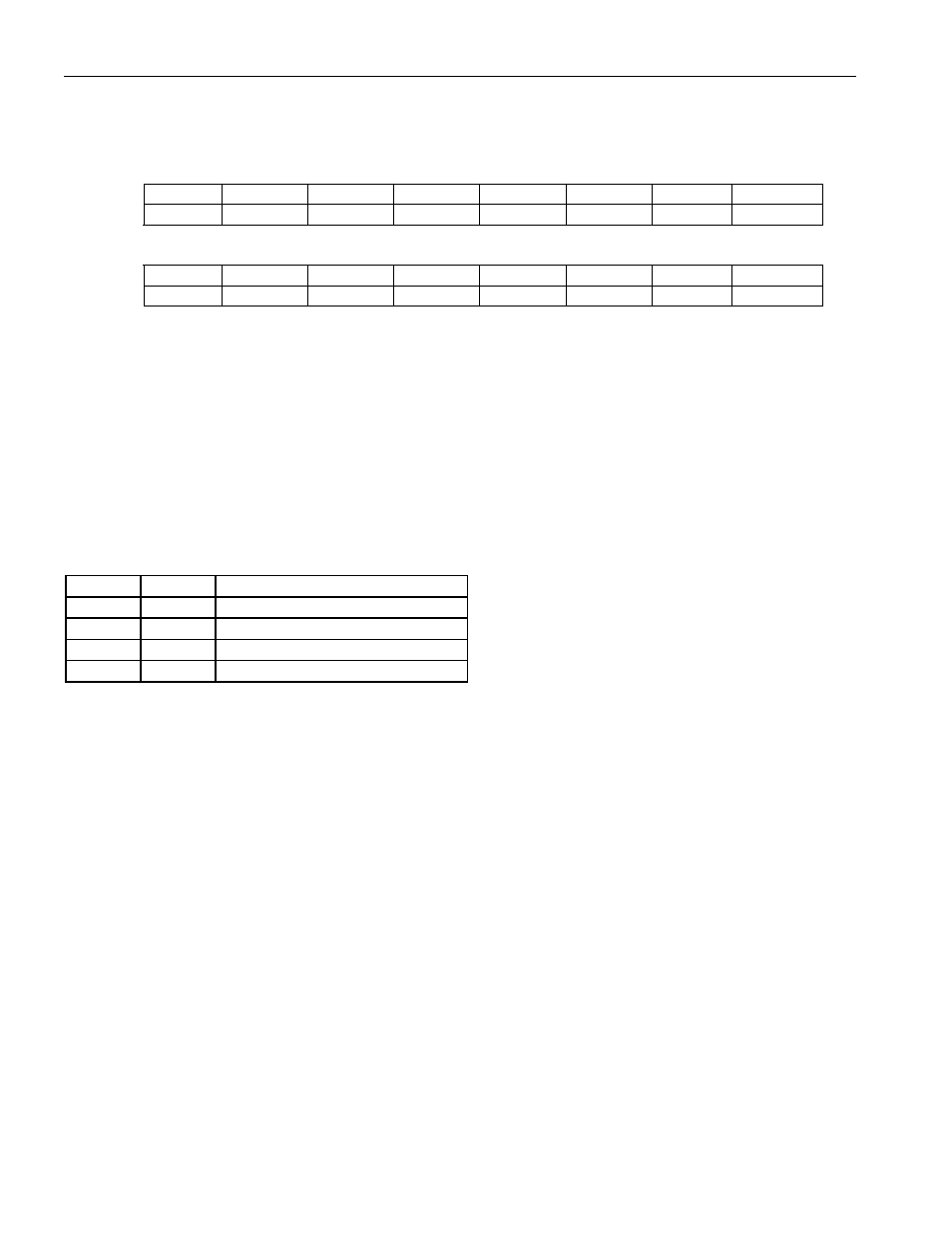

Register Name:

THCD

Register Description: Transmit HDLC Channel Definition

Register Address:

0484h

Bit

# 7 6 5 4 3 2 1 0

Name TABTE

TCFCS TBF TID TCRC1

TCRC0

TIFS

TTRANS

Default

Bit

# 15 14 13 12 11 10 9 8

Name n/a n/a

n/a

TZSD TFG3 TFG2 TFG1 TFG0

Default

Note: Bits that are underlined are read only, all other bits are read-write.

Bit 0/Transmit Transparent Enable (TTRANS). When this bit is set low, the HDLC engine generates flags and

the FCS (if enabled through TCRC0/1) and performs zero stuffing. When this bit is set high, the HDLC controller

does not generate flags or the FCS and does not perform zero stuffing.

0 = transparent mode disabled

1 = transparent mode enabled

Bit 1/Transmit Interfill Select (TIFS)

0 = the interfill byte is 7Eh (01111110)

1 = the interfill byte is FFh (11111111)

Bits 2, 3/Transmit CRC Selection (TCRC0/TCRC1). These bits are ignored if the HDLC channel is set to

transparent mode (TTRANS = 1).

TCRC1 TCRC0

ACTION

0

0

No CRC is generated

0

1

16-bit CRC (CCITT/ITU Q.921)

1 0

32-bit

CRC

1 1

Illegal

state

Bit 4/Transmit Invert Data Enable (TID). When this bit is set low, the outgoing HDLC packets are not inverted

after being generated. When this bit is set high, the HDLC engine inverts all the data (flags, information fields, and

FCS) after the packet has been generated.

0 = do not invert data

1 = invert all data (including flags and FCS)

Bit 5/Transmit Bit Flip (TBF). When this bit is set low, the HDLC controller obtains the first HDLC bit to be

transmitted from the lowest bit position of the PCI bus bytes (i.e., PAD[0], PAD[8], PAD[16], PAD[24]). When

this bit is set high, the HDLC engine obtains the first HDLC bit to be transmitted from the highest bit position of

the PCI bus bytes (i.e., PAD[7], PAD[15], PAD[23], PAD[31]).

0 = the first HDLC bit transmitted is obtained from the lowest bit position of the bytes on the PCI bus

1 = the first HDLC bit transmitted is obtained from the highest bit position of the bytes on the PCI bus

Bit 6/Transmit Corrupt FCS (TCFCS). When this bit is set low, the HDLC engine allows the frame checksum

sequence (FCS) to be transmitted as generated. When this bit is set high, the HDLC engine inverts all the bits of

the FCS before transmission occurs. This is useful in debugging and testing HDLC channels at the system level.

0 = generate FCS normally

1 = invert all FCS bits

Bit 7/Transmit Abort Enable (TABTE). When this bit is set low, the HDLC engine performs normally, only

sending an abort sequence (eight 1s in a row) when an error occurs in the PCI block or the FIFO underflows.

When this bit is set high, the HDLC engine continuously transmits an all-ones pattern (i.e., an abort sequence).

This bit is still active when the HDLC engine is configured in the transparent mode (TTRANS = 1).