Rainbow Electronics DS31256 User Manual

Page 49

DS31256

49 of 181

Bit 8/Port 0 High-Speed Mode (RP0 (1, 2) HS). If enabled, the port 0 (1, or 2) Layer 1 state machine logic is

defeated, and RC0 (1, 2) and RD0 (1, 2) are routed to some dedicated high-speed HDLC processing logic. Only

present in RP0CR, RP1CR and RP2CR. Bit 8 is not assigned in ports 3 through 15.

0 = disabled

1 = enabled

Bit 9/Unchannelized Enable (RUEN). When enabled, this bit forces the port to operate in an unchannelized

fashion. When disabled, the port operates in a channelized mode.

0 = channelized mode

1 = unchannelized mode

Bit 10/Local Loopback Enable (LLB). This loopback routes transmit data back to the receive port. It can be used

in both channelized and unchannelized port operating modes, even on ports 0, 1, and 2 operating at speeds up to

52MHz (

). In channelized applications, a per-channel loopback can be realized by using the channelized

local loopback (CLLB) function. See Section

for details on CLLB.

0 = loopback disabled

1 = loopback enabled

Bit 12/V.54 Time Out (VTO). This read-only bit reports the real-time status of the V.54 detector. It is set to 1

when the V.54 detector has finished searching for the V.54 loop-up pattern and has not detected it. This indicates

to the host that the V.54 detector can now be used to search for the V.54 loop-up pattern on other HDLC channels,

and the host can initiate this by configuring the RV54 bits in the RP[n]CR register and then toggling the VRST

control bit. See Section

for more details about how the V.54 detector operates.

Bit 13/V.54 Loopback (VLB). This read-only bit reports the real-time status of the V.54 detector. It is set to 1

when the V.54 detector has verified that a V.54 loop-up pattern has been seen. When set, it remains set until either

the V.54 loop-down pattern is seen or the V.54 detector is reset by the host (i.e., by toggling VRST). See

Section

for more details on how the V.54 detector operates.

Bit 14/Interrupt Enable for RCOFA (IERC)

0 = interrupt masked

1 = interrupt enabled

Bit 15/COFA Status Bit (RCOFA). This latched read-only status bit sets if a COFA is detected. The COFA is

detected by sensing that a sync pulse has occurred during a clock period that was not the first bit of the

193/256/512/1024-bit frame. This bit resets when read and does not set again until another COFA has occurred.

Transmit Side Control Bits (one each for all 16 ports)

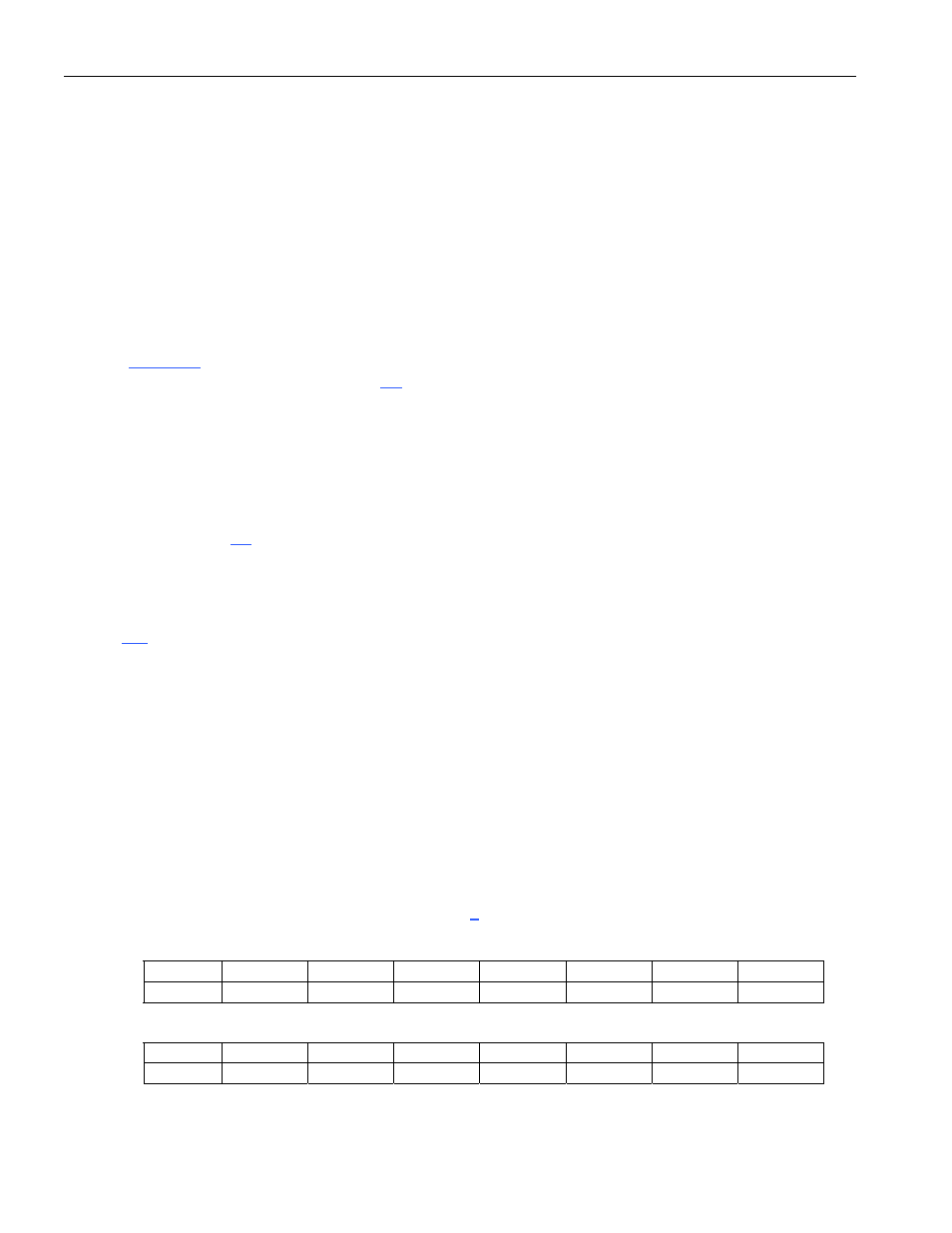

Register Name:

TP[n]CR, where n = 0 to 15 for each port

Register Description: Transmit Port [n] Control Register

Register Address:

See the Register Map in Section

Bit

# 7 6 5 4 3 2 1 0

Name

TSS1 TSS0 TSD1 TSD0

TFDA1

TISE TIDE TICE

Default

0 0 0 0 0 0 0 0

Bit

# 15 14 13 12 11 10 9 8

Name TCOFA

IETC n/a n/a TUBS UNLB TUEN

TP[i]HS

Default

0 0 0 0 0 0 0 0

Note: Bits that are underlined are read-only; all other bits are read-write.