Detailed description, Table 1-a. data sheet definitions – Rainbow Electronics DS31256 User Manual

Page 7

DS31256

7 of 181

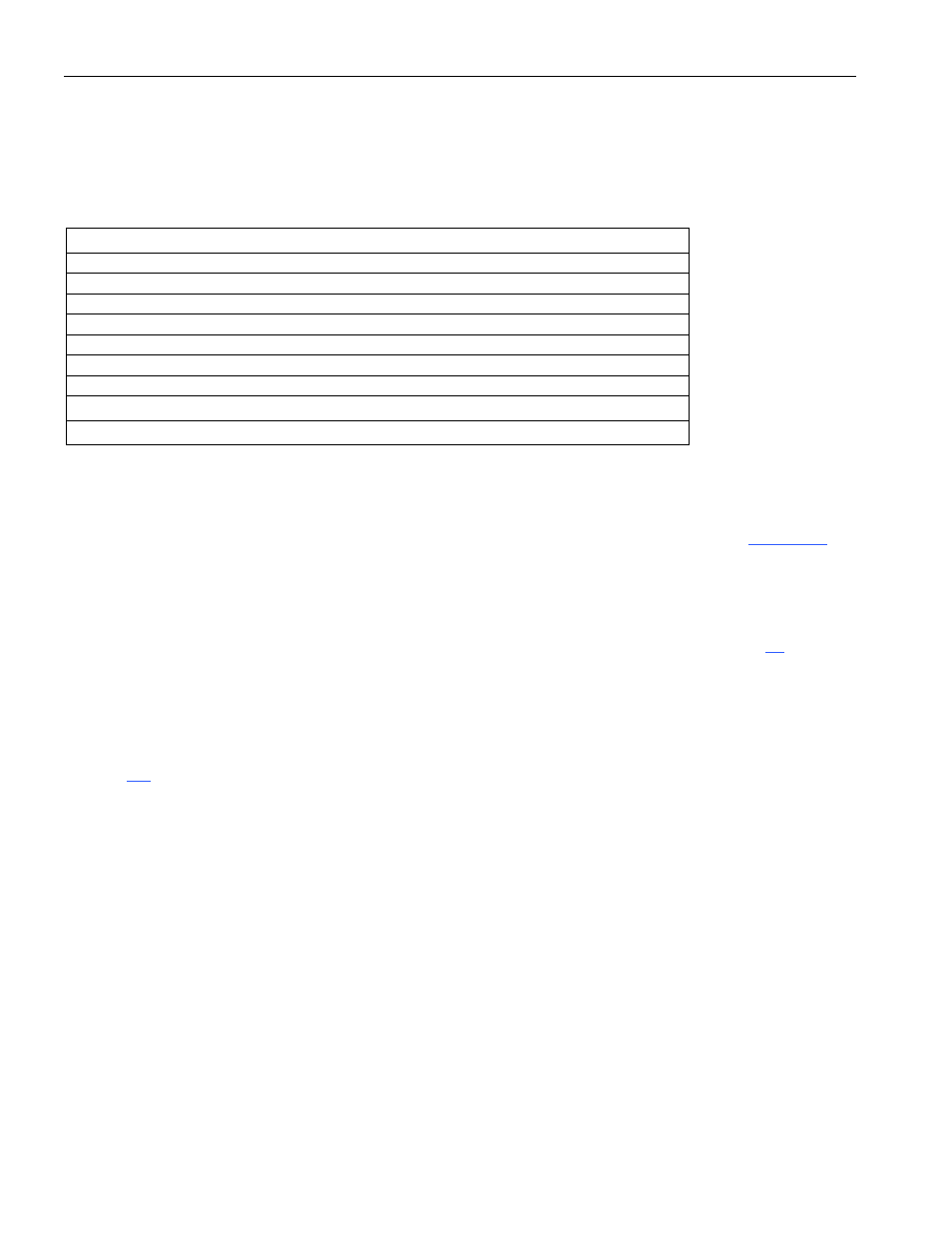

Table 1-A. Data Sheet Definitions

The following terms are used throughout this data sheet.

Note: The DS31256’s ports are numbered 0 to 39; the HDLC channels are numbered 1 to 40. HDLC Channel 1 is always associated with Port

0, HDLC Channel 2 with Port 1, and so on.

TERM DEFINITION

BERT

Bit Error-Rate Tester

Descriptor

A message passed back and forth between the DMA and the host

Dword

Double word; a 32-bit data entity

DMA Direct

Memory

Access

FIFO

First In, First Out. A temporary memory storage scheme.

HDLC

High-Level Data-Link Control

Host

The main controller that resides on the PCI Bus

n/a Not

assigned

V.54

A pseudorandom pattern that controls loopbacks (see ANSI T1.403)

2. DETAILED DESCRIPTION

This data sheet is broken into sections detailing each of the DS31256 Envoy’s blocks. See

a block diagram.

The Layer 1 block handles the physical input and output of serial data to and from the DS31256. The

DS31256 is capable of handling up to 64 T1 or E1 data streams or two T3 data streams simultaneously.

Each of the 16 physical ports can handle up to two or four T1 or E1 data streams. Section

details a

few common applications for the DS31256. The Layer 1 block prepares the incoming data for the HDLC

block and grooms data from the HDLC block for transmission. The block can perform both channelized

and unchannelized loopbacks as well as search for V.54 loop patterns. It is in the Layer 1 block that the

host enables HDLC channels and assigns them to a particular port and/or DS0 channel(s). The host

assigns HDLC channgels through the R[n]CFG[j] and T[n]CFG[j] registers, which are described in

Section

. The Layer 1 block interfaces directly to the BERT block. The BERT block can generate and

detect both pseudorandom and repeating bit patterns and is used to test and stress data communication

links.

The HDLC Block consists of two types of HDLC controllers. There are 16 Slow HDLC Engines (one

for each port) that are capable of operating at speeds up to 8.192 Mbps in channelized mode and up to

10 Mbps in unchannelized mode. There are also three Fast HDLC Engines, which only reside on Ports

0, 1 and 2 and they are capable of operating at speeds up to 52 Mbps. Via the RP[n]CR and TP[n]CR

registers in the Layer One Block, the Host will configure Ports 0, 1, and 2 to use either the Slow or the

Fast HDLC engine. The HDLC Engines perform all of the Layer 2 processing, including zero stuffing

and destuffing, flag generation and detection, CRC generation and checking, abort generation and

checking.