11 move, Move, Register address field definitions (load64 format) – Avago Technologies LSI53C1010 User Manual

Page 82

3-42

The SCSI SCRIPTS Processor Instruction Set

Description

The LOAD64 instruction is more efficient than a Move Memory

instruction when moving data from a memory location to an internal

register of the chip. It is a two Dword instruction, compared to three

Dwords for a Memory Move. This instruction may be used to move up to

4 bytes. The number of bytes being loaded is indicated by the low order

bits in the first Dword of the instruction. The maximum number of bytes

is defined by the Register Address field, as illustrated in

.

Notes

The register address and memory address must have the same byte

alignment, and the byte count set so that it does not cross Dword

boundaries. The memory address may not map back to the SCRIPTS

processor operating registers, although it may map back to a location in

the SCRIPTS RAM. If these conditions are violated, a PCI illegal

read/write cycle will occur and the chip will issue an Interrupt (Illegal

Instruction Detected) immediately following, because the intended

operation did not happen.

Legal Forms

LOAD64 register, byte_count, source_address

LOAD64 register, byte_count, DSAREL(source_address)

3.2.11 MOVE

MOVE {FROM | count,} [PTR] address, {WITH | WHEN}phase

Supported by

All LSI Logic SCSI SCRIPTS Processors.

Definition

SCSI Block Move.

Operands

This command has the following operands:

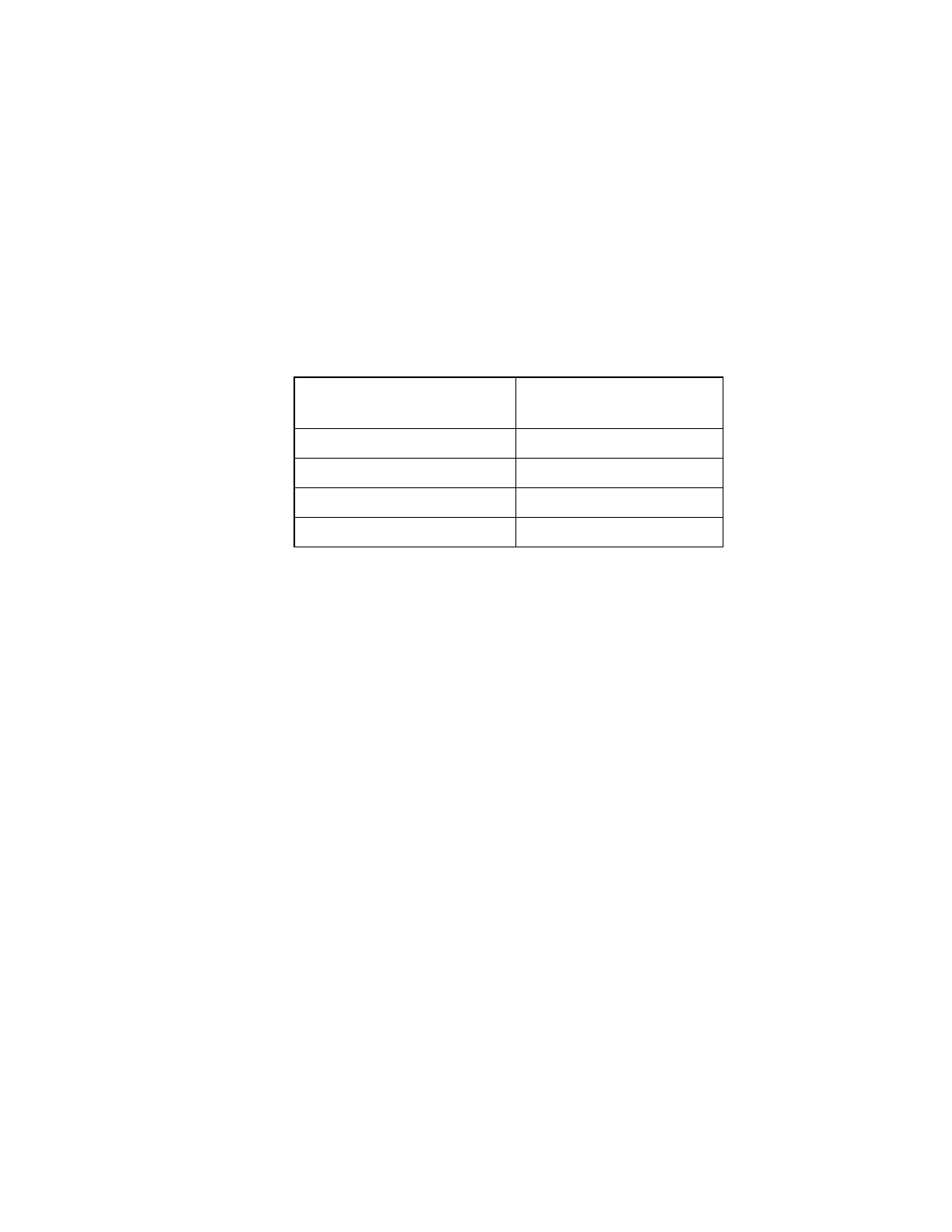

Table 3.12

Register Address Field Definitions (LOAD64 Format)

DBC Bits [17:16]

(Register Address bits [A1:A0])

Number of Bytes to Load

00

1, 2, 3, or 4

01

1, 2, or 3

10

1 or 2

11

1