Avago Technologies LSI53C1010 User Manual

Page 166

6-16

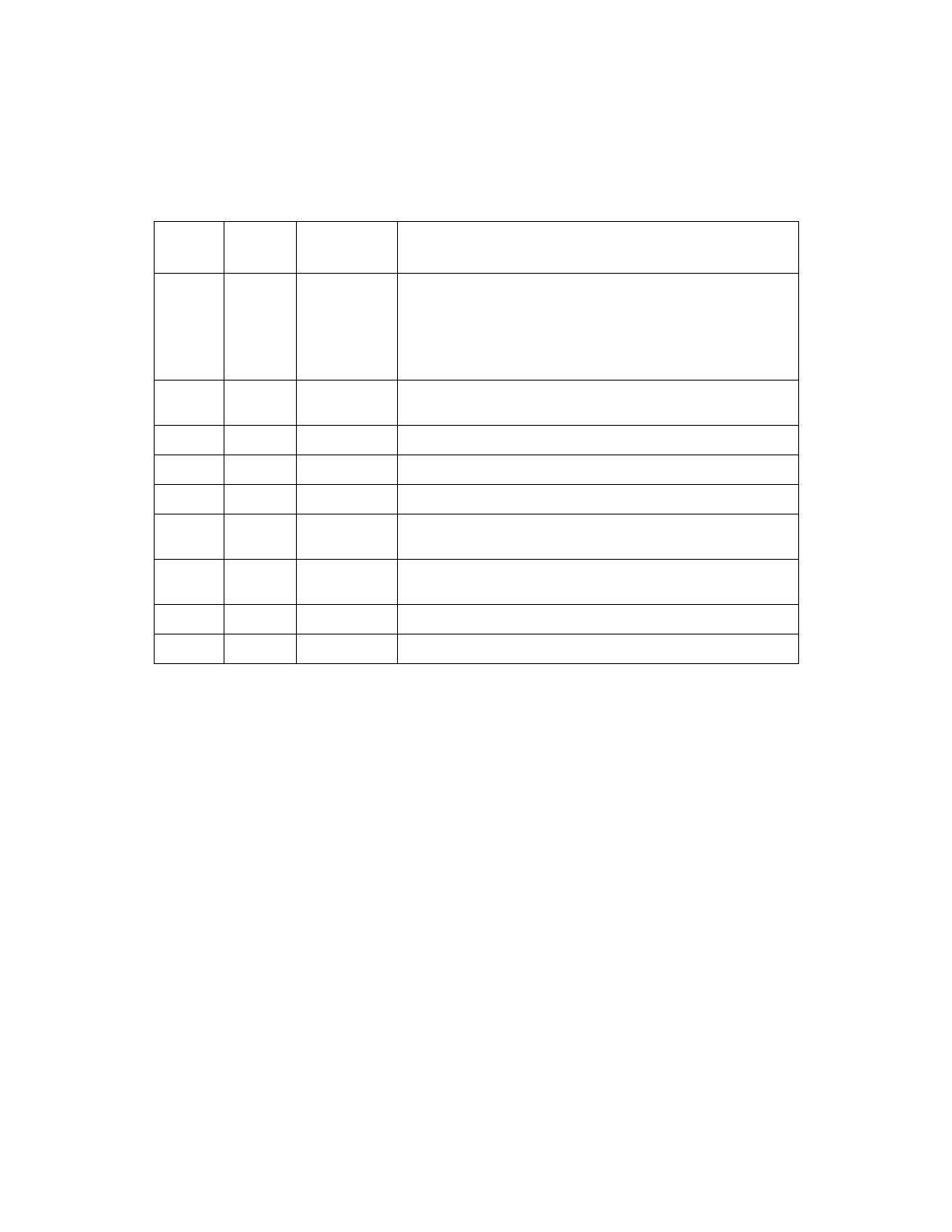

Using the Registers to Control Chip Operations

0x46

MACNTL

3, 2, 1, 0

Initialize these when using the MAC_TESTOUT pin. These bits

determine local or remote access for the following operations:

Bit 3: Data write

Bit 2: Data read

Bit 1: SCRIPTS pointers

Bit 0: SCRIPTS fetch

0x48

STIME0

[7:4], [3:0]

Bits [7:4]: Handshake-to-Handshake Timer Period

Bits [3:0]: Selection Time-Out

0x49

STIME1

[3:0]

Bits [3:0]: General Purpose Timer Period

0x4A

RESPID0 all

N/A

0x4B

RESPID1 all

N/A

0x4D

STEST1

7, [3:2]

Bit 7: SCLK

Bits [3:2]: SCSI Clock Doubler 1–0 (LSI53C875 only)

0x4E

STEST2

5, 1

Bit 5: SCSI Differential Mode

Bit 1: Extend REQ/ACK Filtering

0x4F

STEST3

7

Bit 7: TolerANT Enable

0xBC

SCNTL4

7

Bit 7: Ultra3 Transfer Enable

Table 6.10

LSI53C825A/875/876/885/895/895A/896/10XX Startup Bits (Cont.)

Register

Address

Register

Name

Bits

Remarks