Avago Technologies LSI53C1010 User Manual

Page 291

A-11

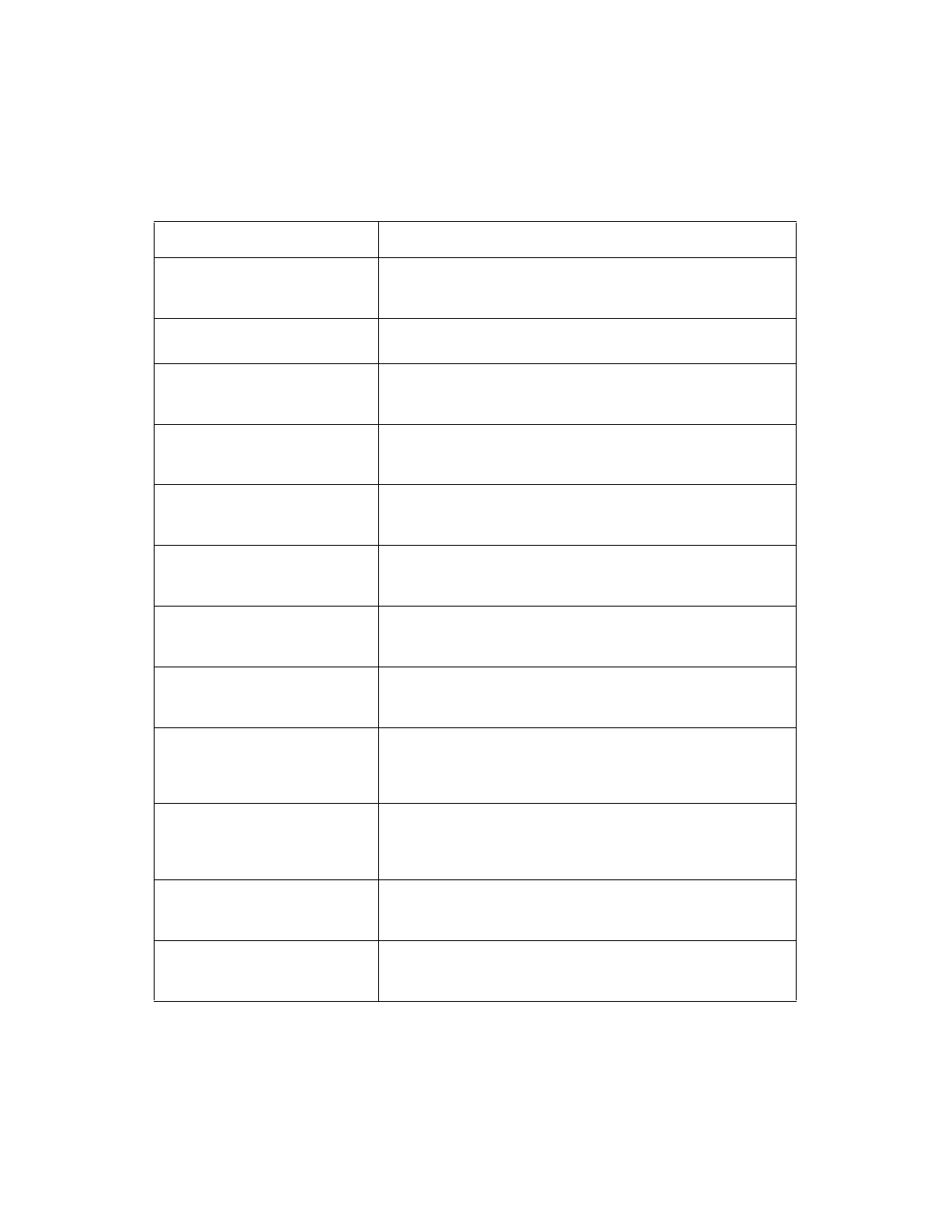

SHR LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The shift right instruction is only supported on LSI53C720 and

higher architectures.

SIEN LSI53C700 and LSI53C710

architectures only

The SIEN register is only available on the LSI53C700/710

architectures.

SIEN0 LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The SIEN0 register is only available on the LSI53C720 and

higher architectures.

SIEN1 LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The SIEN1 register is only available on the LSI53C720 and

higher architectures.

SIST0 LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The SIST0 register is only available on the LSI53C720 and

higher architectures.

SIST1 LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The SIST1 register is only available on the LSI53C720 and

higher architectures.

SLPAR LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The SLPAR register is only available on the LSI53C720 and

higher architectures.

SODL LSI53C700, LSI53C710,

and LSI53C81X architectures

only

The SODL register is one byte only on the LSI53C700,

LSI53C710, and LSI53C81X chips.

SODL0 LSI53C720, LSI53C770,

LSI53C82X, LSI53C875,

LSI53C876, LSI53C885, and

LSI53C895 architectures only

The SODL register is two bytes on the chips that support Wide

SCSI.

SODL1 LSI53C720, LSI53C770,

LSI53C82X, LSI53C875,

LSI53C876, LSI53C885, and

LSI53C895 architectures only

The SODL register is two bytes on the chips that support Wide

SCSI.

SSID LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The SSID register is only available on the LSI53C720 and higher

architectures.

STEST0 LSI53C720, LSI53C770,

and LSI53C8XX architectures

only

The STEST0 register is only available on the LSI53C720 and

higher architectures.

Table A.1

NASM Error Messages (Cont.)

Error

Description