5 big and little endian byte addressing, Table 2.6 big and little endian byte addressing, 1 scripts instruction sequence – Avago Technologies LSI53C1010 User Manual

Page 38: Big and little endian byte addressing, Scripts instruction sequence

2-8

Programming with SCRIPTS

2.5 Big and Little Endian Byte Addressing

The guidelines in this section will help assure proper byte lane ordering

in big or little endian designs. Please check the technical manual for each

chip to determine whether your product supports big and/or little endian

addressing. The later series of chips that have 64-bit addressing are all

little endian.

Big endian addressing is used primarily in designs based on Motorola

processors. The SCRIPTS processor treats D[31:24] as the lowest

physical memory address. Little endian is used primarily in designs

based on Intel processors and treats D[7:0] as the lowest physical

memory address.

describes big and little endian byte addressing.

2.5.1 SCRIPTS Instruction Sequence

To ensure that SCSI SCRIPTS instructions are in the correct order, each

SCRIPTS routine must be compiled in the target architecture. The “C”

output file (

.OUT

) lists arrays of Dword values, which are stored in

memory by the processor in the correct order for their subsequent

execution. Execution of a little endian SCRIPTS instruction on a big

endian machine requires reversal of the bytes before execution. The best

way to guarantee correct byte ordering is to make sure the SCRIPTS are

placed in memory with the opcode byte on the same byte lane as the

Data Command (DCMD) register. A PROM cannot be moved from one

environment to another without reordering bytes within each word.

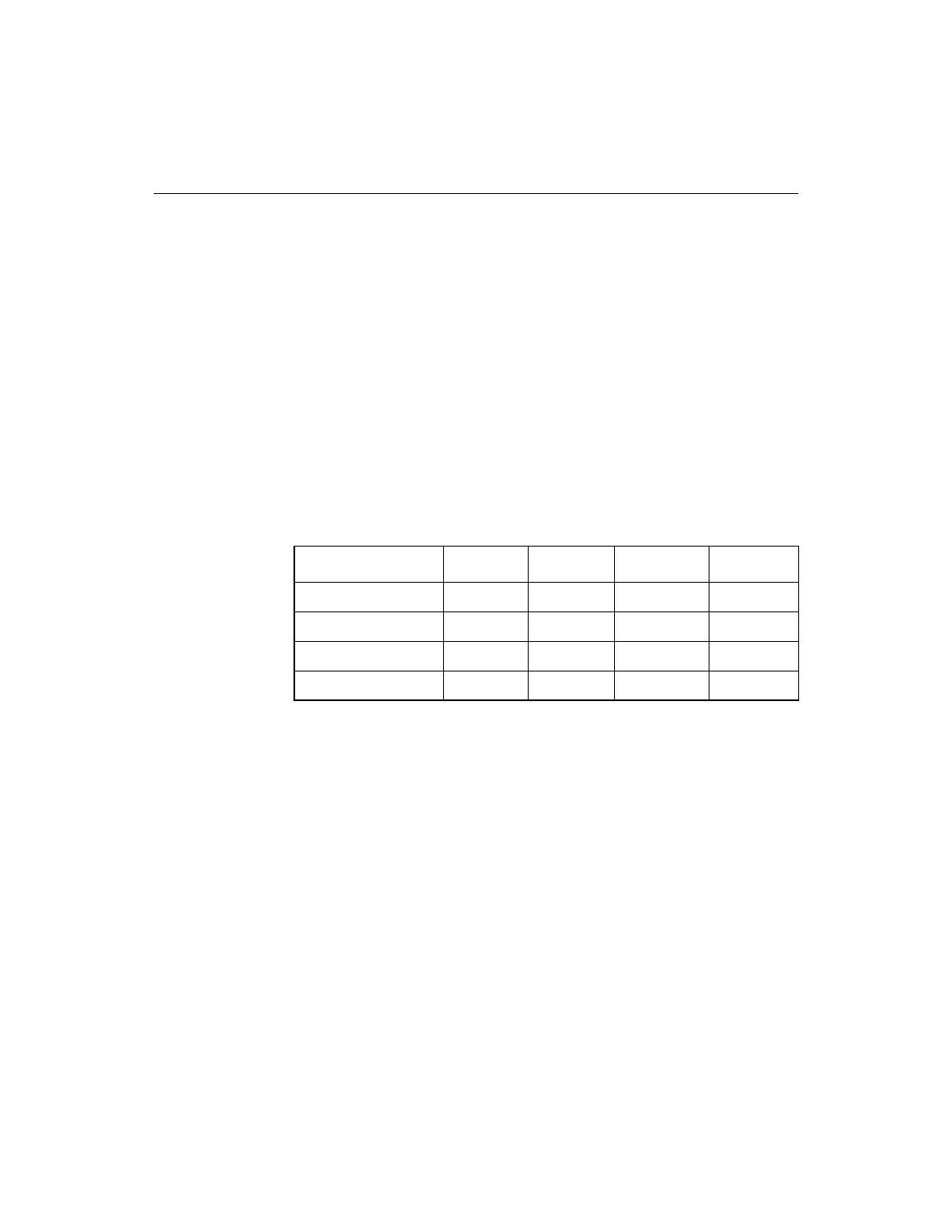

Table 2.6

Big and Little Endian Byte Addressing

System Data Bus

[31:24]

[23:16]

[15:8]

[7:0]

P

ins

[31:24]

[23:16]

[15:8]

[7:0]

Register

SCNTL3

SCNTL2

SCNTL1

SCNTL0

Little Endian Address

0x03

0x02

0x01

0x00

Big Endian Address

0x00

0x01

0x02

0x03