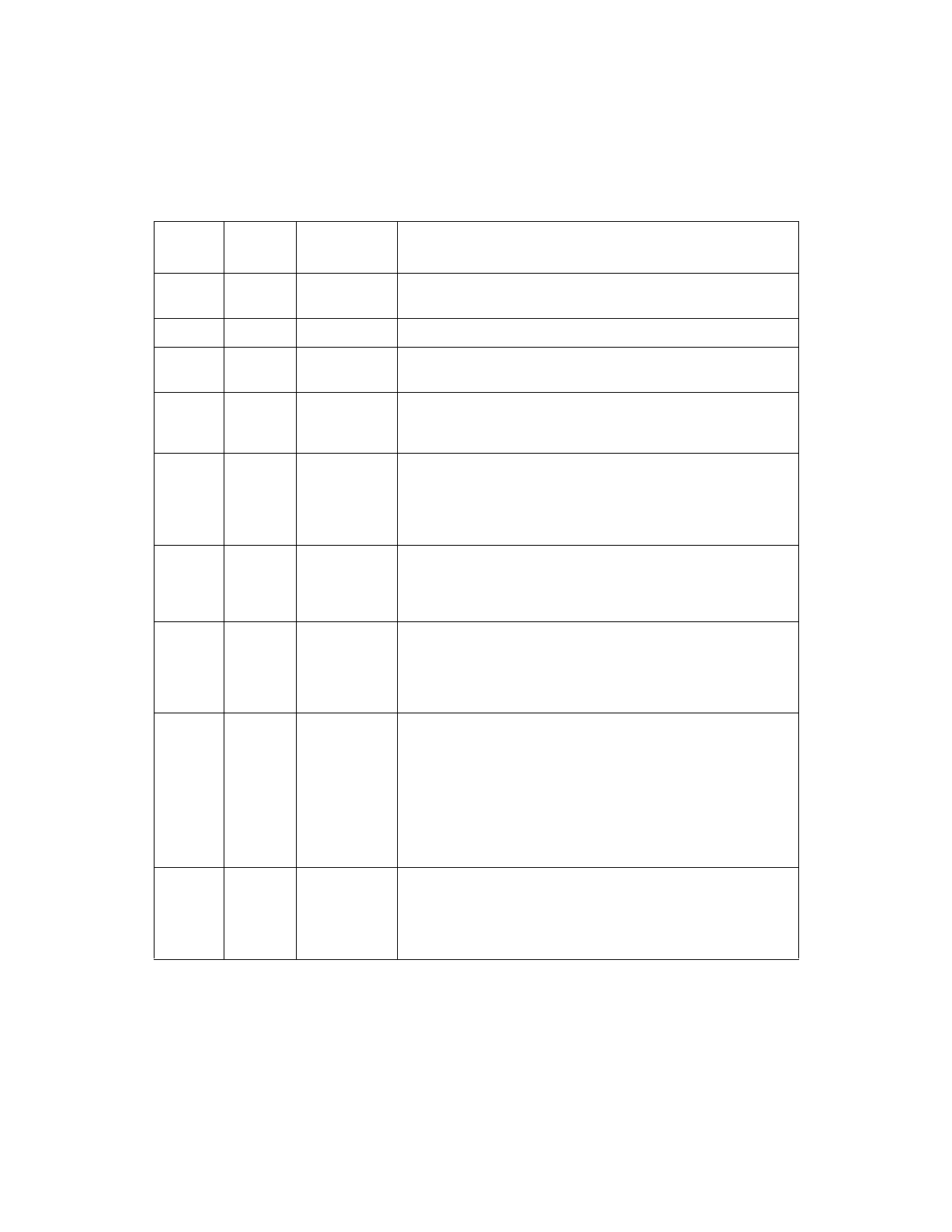

Avago Technologies LSI53C1010 User Manual

Page 165

Register Initialization

6-15

0x21

CTEST4

7, 3

Bit 7: Burst Disable

Bit 3: Master Parity Error Enable

0x22

CTEST2

3

SCRATCHA/B operation (when SCRIPTS RAM is enabled).

0x18

CTEST0

[2:0]

Set the priority level for gaining access to the PCI bus

(LSI53C885 only).

0x2C–

0x2F

DSP

all

At the end of the initialization program, write the address of the

first SCRIPTS instruction to this register to begin SCRIPTS

execution.

0x38

DMODE

[7:6], 5, 4, 3,

2

Bits [7:6]: Burst Length

Bit 5: Source I/O-Memory Enable

Bit 4: Destination I/O-Memory Enable

Bit 3: Enable Read Line

Bit 2: Enable Read Multiple

0x39

DIEN

4, 3, 2, 0

Bit 4: Aborted

Bit 3: Single Step Interrupt

Bit 2: SCRIPTS Interrupt Instruction Received

Bit 0: Illegal Instruction Detected

0x3B

DCNTL

7, 5, 4, 3, 0

Bit 7: Cache Line Size Enable

Bit 5: Prefetch Enable

Bit 4: Single Step Mode

Bit 3: IRQ Mode

Bit 0: LSI53C700 Compatibility

0x40

SIEN0

7, 6, 5, 4, 3,

2, 1, 0

Interrupt mask bits for:

Bit 7: Phase Mismatch or SATN/

Bit 6: Function Complete

Bit 5: Selected

Bit 4: Reselected

Bit 3: SCSI Gross Error

Bit 2: Unexpected Disconnect

Bit 1: SCSI Reset Condition

Bit 0: SCSI Parity Error

0x41

SIEN1

4, 2, 1, 0

Interrupt mask bits for:

Bit 4: SCSI Bus Mode Change (LSI53C895 only)

Bit 2: Selection or Reselection Time-out

Bit 1: General Purpose Timer Expired

Bit 0: Handshake-to-Handshake Timer Expired

Table 6.10

LSI53C825A/875/876/885/895/895A/896/10XX Startup Bits (Cont.)

Register

Address

Register

Name

Bits

Remarks