6 interrupt registers, Table 6.5 interrupt registers, Interrupt registers – Avago Technologies LSI53C1010 User Manual

Page 157: Section 6.6

Interrupt Registers

6-7

6.6 Interrupt Registers

lists the Interrupt registers. Interrupt registers contain interrupt

status information. The DSTAT contains the DMA interrupt status

information. The SIST0 and SIST1 contain SCSI interrupt status bits. The

remaining registers contain interrupt enable bits. The ISTAT register can

be polled for interrupts. It is the only register that can be accessed while

SCRIPTS is running. Refer to

Chapter 9, “SCRIPTS Programming

for more information on handling interrupts.

CCNTL3

2

Chip Control 3 Skew Control, LVD Drive Strength Control.

MMRS

1

Memory Move

Read Selector

Supplies AD[63:32] during data read operations for Memory-to-Memory

Move and absolute address LOAD operations.

MMWS

1

Memory Move

Write Selector

Supplies AD[63:32] during data write operations during Memory-to-

Memory Moves and absolute address STORE operations.

1. LSI53C895 and later only.

2. LSI53C10XX only.

Table 6.4

64-Bit Selector Registers (Cont.)

Name

Definition

Functions

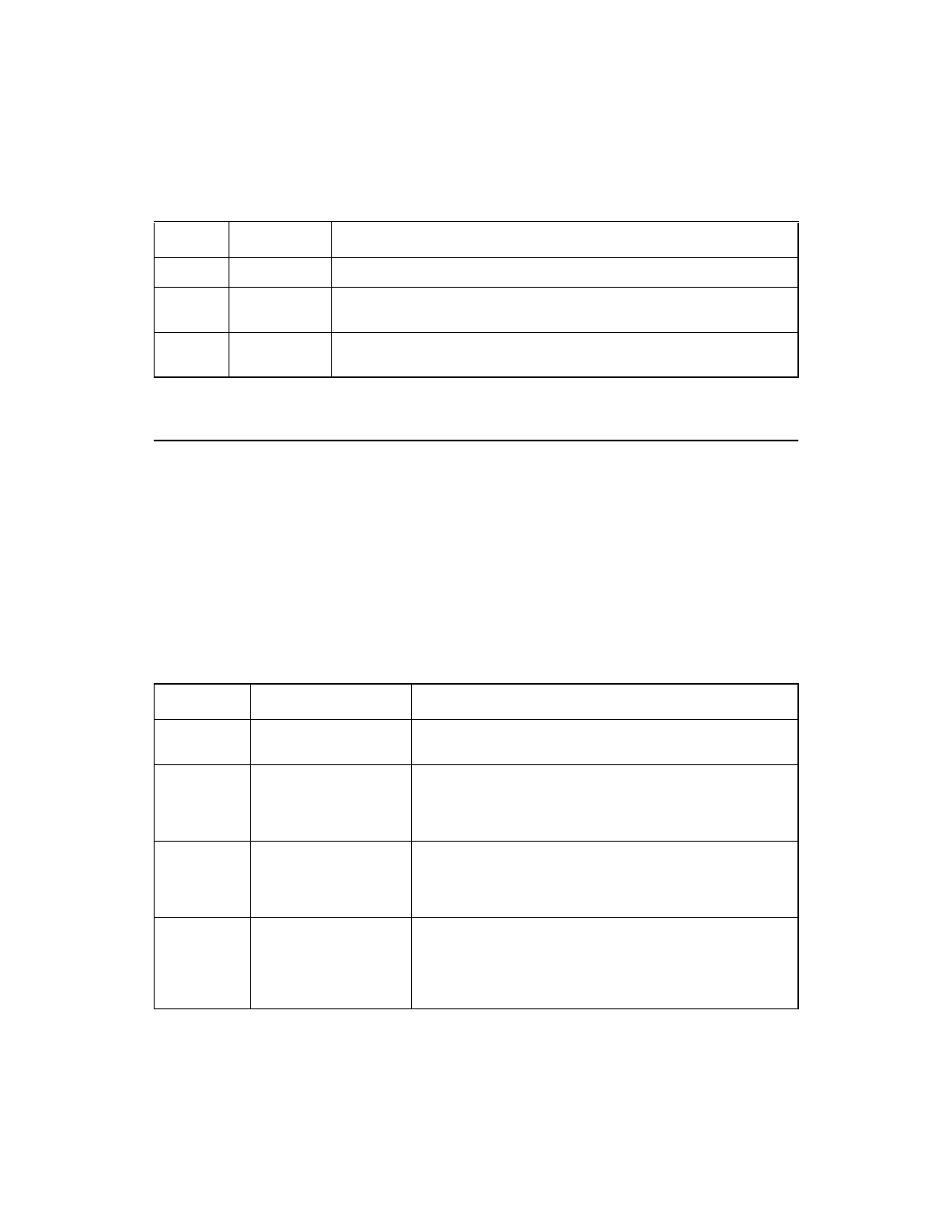

Table 6.5

Interrupt Registers

Name

Definition

Functions

CSO

1

Current Inbound SCSI

Offset

Indicates current SCSI offset.

DIEN

DMA Interrupt Enable

Contains interrupt mask bits corresponding to master data

parity error, bus fault, aborted operation, single step

interrupt, SCRIPTS interrupt instruction received, illegal

instruction detected.

DSTAT

DMA Status

Reports sources of DMA interrupts: DMA FIFO empty,

Master data parity error, bus fault, aborted, single step

interrupt, SCRIPTS interrupt instruction received, illegal

instruction detected.

ISTAT

2

Interrupt Status

Interrupt polling; determines whether a SCSI or DMA

interrupt has occurred; checks for stacked interrupts; aborts

an operation; software reset; signal process bit; semaphore

bit; interrupt on the fly bit; indicate SCSI interrupt pending

(LSI53C885 only).