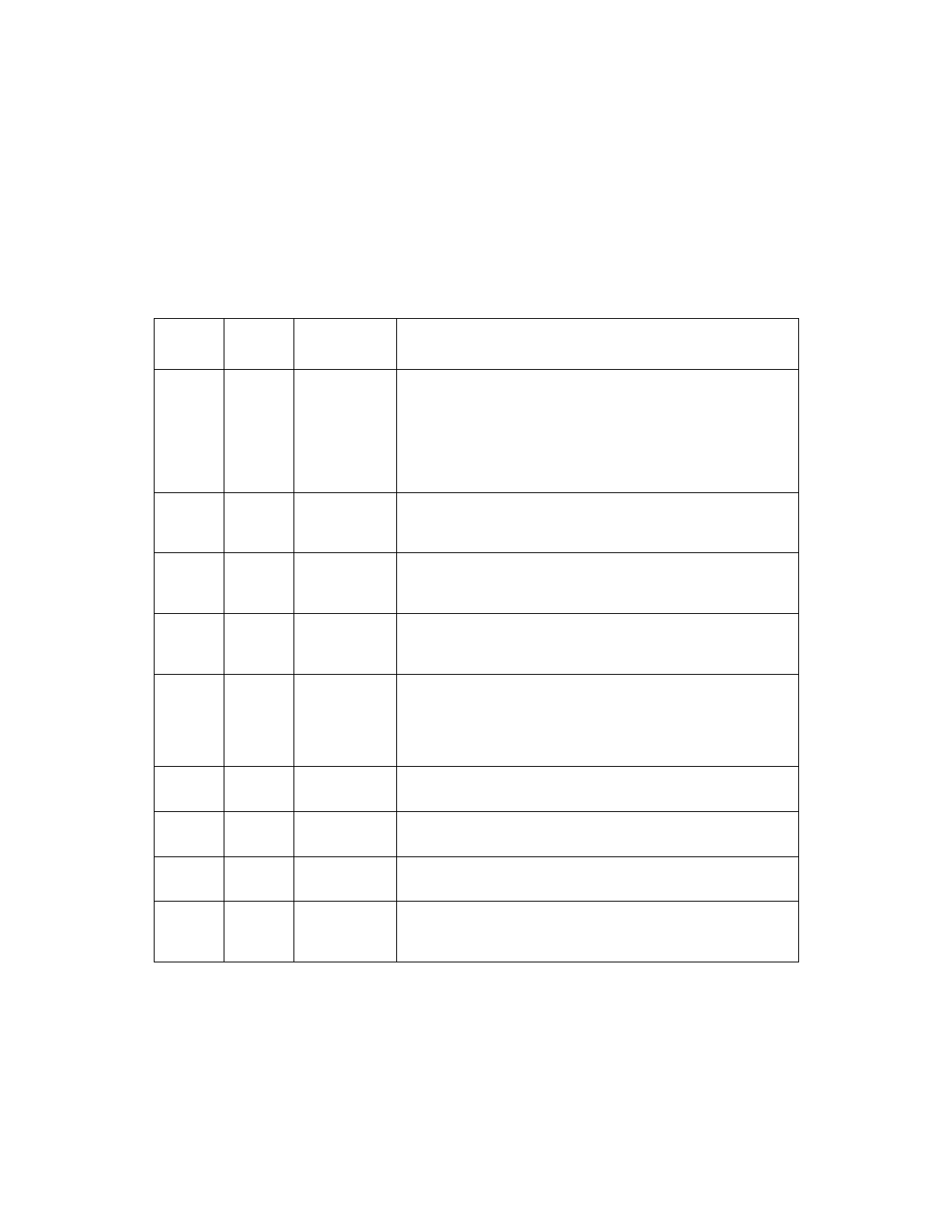

Table 6.9 lsi53c815/810a/860 startup bits, Lsi53c815/810a/860 startup bits, Table 6.9 – Avago Technologies LSI53C1010 User Manual

Page 162

6-12

Using the Registers to Control Chip Operations

contains a section on the bits and registers that affect parity

checking and generation. All reserved bits should be left cleared by the

startup program.

Table 6.9

LSI53C815/810A/860 Startup Bits

Register

Address

Register

Name

Bits

Remarks

0x00

SCNTL0

[7:6], 3, [1:0]

Bits [7:6]: Arbitration Mode

Bit 3: Enable Parity Checking

Bit 1: Assert SATN/ on Parity Error

Bit 0: Target Mode. Bit 0 can be set either at initialization or

during SCRIPTS operation. Set it at startup if the chip

operates as a target only. If it switches between Target and

Initiator Modes, use SCRIPTS to control this bit.

0x01

SCNTL1

7, 5

Bit 7: Extra Clock Cycle of Data Setup

Bit 5: Disable Halt on Parity Error or SATN/ (for Target Mode

only)

0x03

SCNTL3

7, [6:4], [2:0]

Bit 7: Ultra Enable (LSI53C860 only)

Bits [6:4]: Synchronous Clock Conversion Factor

Bits [2:0]: Clock Conversion Factor

0x04

SCID

6, 5, [2:0]

Bit 6: Enable Response to Reselection

Bit 5: Enable Response to Selection

Bits [2:0]: Encoded Chip SCSI ID

0x05

SXFER

[7:5], [3:0]

Since the default operation for SCSI is asynchronous transfers,

these bits should probably not be set until synchronous

parameters are established between the initiator and target.

Bits [7:5]: Synchronous Transfer Period

Bits [3:0]: Max SCSI Synchronous Offset

0x10–

0x13

DSA

all

Must be initialized to use Table Indirect Mode.

0x1B

CTEST3

1, 0

Bit 1: Fetch Pin Mode

Bit 0: Write and Invalidate Enable (LSI53C810A/860 only)

0x21

CTEST4

7, 3

Bit 7: Burst Disable

Bit 3: Master Parity Error Enable

0x2C–

0x2F

DSP

all

At the end of the initialization program, write the address of the

first SCRIPTS instruction to this register to begin SCRIPTS

execution.