7 phase mismatch registers, Phase mismatch registers – Avago Technologies LSI53C1010 User Manual

Page 158

6-8

Using the Registers to Control Chip Operations

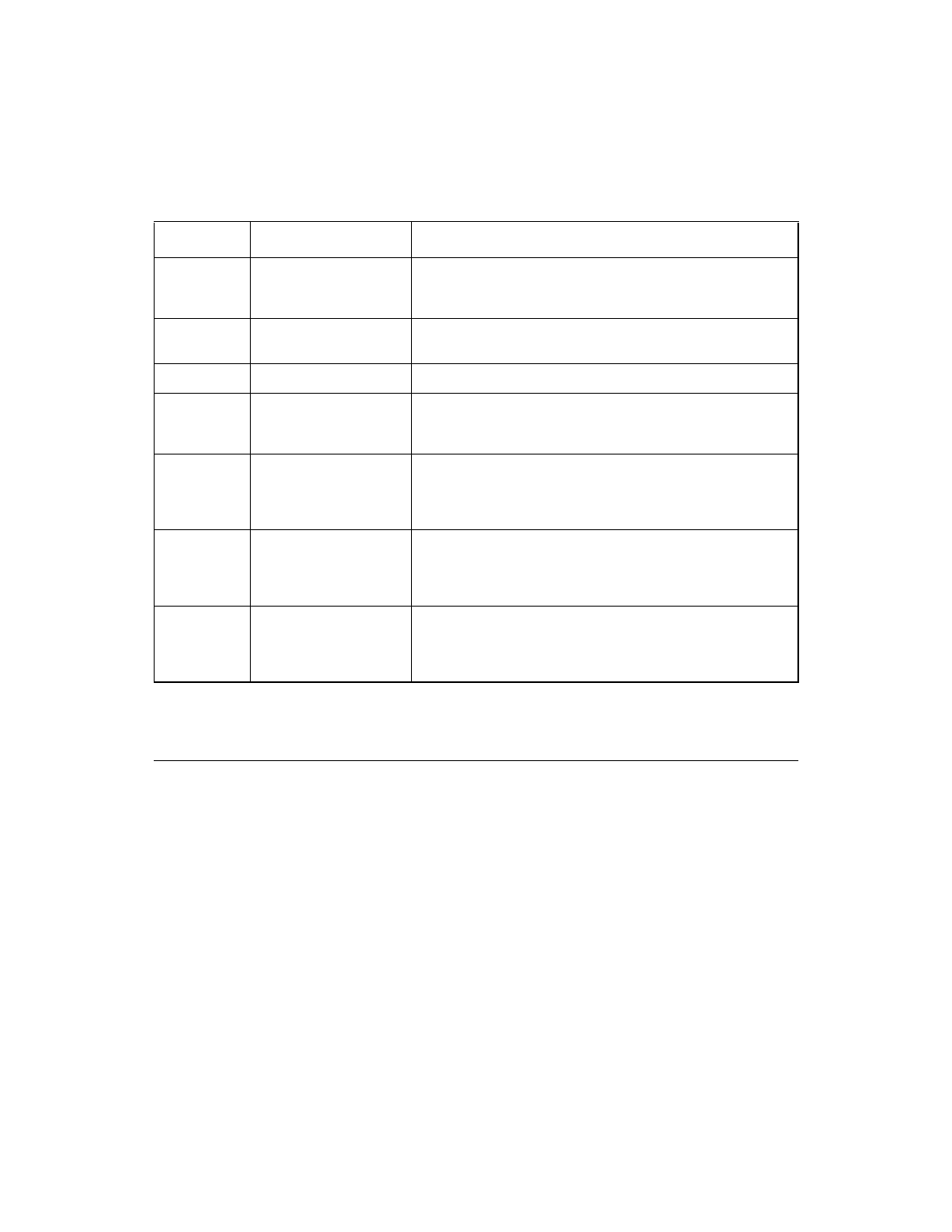

6.7 Phase Mismatch Registers

The Phase Mismatch registers contain information generated during

BMOV instructions, particularly those executing during a phase

mismatch. The Phase Mismatch registers are listed in

. Unless

otherwise noted, these registers are only on LSI53C895 and later chips.

ISTAT0

3

Interrupt Status 0

Abort operation; software reset; semaphore bit; signal

process bit; determines whether a SCSI or DMA interrupt is

pending; SCSI connection.

ISTAT1

3

Interrupt Status 1

Flushing the DMA FIFO; SCRIPTS engine operating; IRQ

pin disable.

MBOX (0, 1)

3

Mailbox

General purpose registers.

SIEN0

SCSI Interrupt Enable 0 Interrupt mask bits for phase mismatch, SATN/, function

complete, selection/reselection, gross error, unexpected

disconnect, SCSI reset, parity error.

SIEN1

SCSI Interrupt Enable 1 Interrupt mask bits for selection/reselection time-out, general

purpose time-out, handshake-to-handshake time-out;

wakeup (LSI53C885 only); SCSI bus mode change

(LSI53C895/896/10XX only).

SIST0

SCSI Interrupt Status 0

Returns the status of the following interrupt conditions:

phase mismatch (SATN/ active), function complete,

selection/reselection, SCSI gross error, unexpected

disconnect, SCSI RST/ received, parity error.

SIST1

SCSI Interrupt Status 1

Returns the status of the following interrupt conditions:

selection/reselection time-out, general purpose timer

expired, handshake-to-handshake timer expired; wakeup

(LSI53C885 only).

1. LSI53C10XX only

2. Up to LSI53C895 only.

3. LSI53C895A and later only.

Table 6.5

Interrupt Registers (Cont.)

Name

Definition

Functions