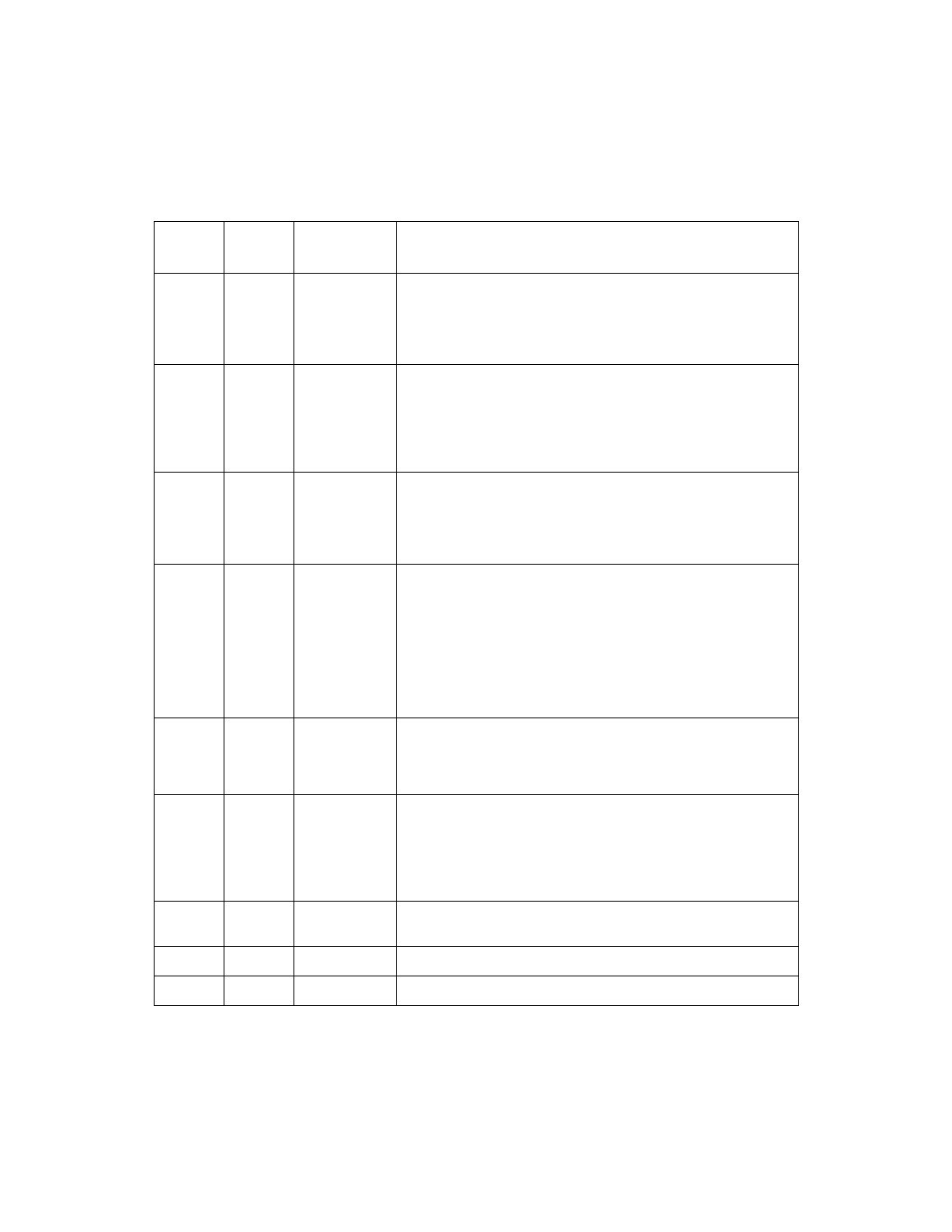

Avago Technologies LSI53C1010 User Manual

Page 163

Register Initialization

6-13

0x38

DMODE

[7:6], 5, 4, 3, 2 Bits [7:6]: Burst Length

Bit 5: Source I/O-Memory Enable

Bit 4: Destination I/O-Memory Enable

Bit 3: Enable Read Line

Bit 2: Enable Read Multiple (LSI53C810A/860 only)

0x39

DIEN

6, 5, 4, 3, 2, 0 Bit 6: Master Data Parity Error

Bit 5: Bus Fault

Bit 4: Aborted

Bit 3: Single Step Interrupt

Bit 2: SCRIPTS Interrupt Instruction Received

Bit 0: Illegal Instruction Detected

0x3B

DCNTL

7, 5, 4, 3, 0

Bit 7: Cache Line Size Enable

Bit 5: Prefetch Enable (LSI53C810A/860 only)

Bit 4: Single Step Mode

Bit 3: IRQ Mode

Bit 0: LSI53C700 Compatibility

0x40

SIEN0

7, 6, 5, 4, 3, 2,

1, 0

Interrupt mask bits for:

Bit 7: Phase Mismatch or SATN/

Bit 6: Function Complete

Bit 5: Selected

Bit 4: Reselected

Bit 3: SCSI Gross Error

Bit 2: Unexpected Disconnect

Bit 1: SCSI Reset Condition

Bit 0: SCSI Parity Error

0x41

SIEN1

2, 1, 0

Interrupt mask bits for:

Bit 2: Selection or Reselection Time-out

Bit 1: General Purpose Timer Expired

Bit 0: Handshake-to-Handshake Timer Expired

0x46

MACNTL 3, 2, 1, 0

Initialize these when using the MAC_TESTOUT pin. These bits

determine local or far access for the following operations:

Bit 3: Data write

Bit 2: Data read

Bit 1: SCRIPTS pointers

Bit 0: SCRIPTS fetches

0x48

STIME0

[7:4], [3:0]

Bits [7:4]: Handshake-to-Handshake Timer Period

Bits [3:0]: Selection Time-out

0x49

STIME1

3–0

Bits [3:0]: General Purpose Timer Period

0x4A

RESPID

all

N/A

Table 6.9

LSI53C815/810A/860 Startup Bits (Cont.)

Register

Address

Register

Name

Bits

Remarks