Figure3.22 wait select format, Wait select format – Avago Technologies LSI53C1010 User Manual

Page 110

3-70

The SCSI SCRIPTS Processor Instruction Set

Example

WAIT SELECT alt_addr

WAIT SELECT REL(alt_addr)

Field(s)

This command has the following fields:

Register

Definition(s)

The information listed below describes the DBC and DSPS registers.

Description

The chip waits for a selection by another device on the SCSI bus. If the

chip is already selected, then the next SCSI SCRIPTS is fetched and

executed. When a bus initiated interrupt or reselect occurs, the chip

changes to the initiator role, fetches the next instruction from the address

pointed to by the 32-bit jump address, and continues execution. If the

SIGP bit in the ISTAT register is set by the host processor, the chip will

also fetch the instruction at the alternate address. The SCRIPTS

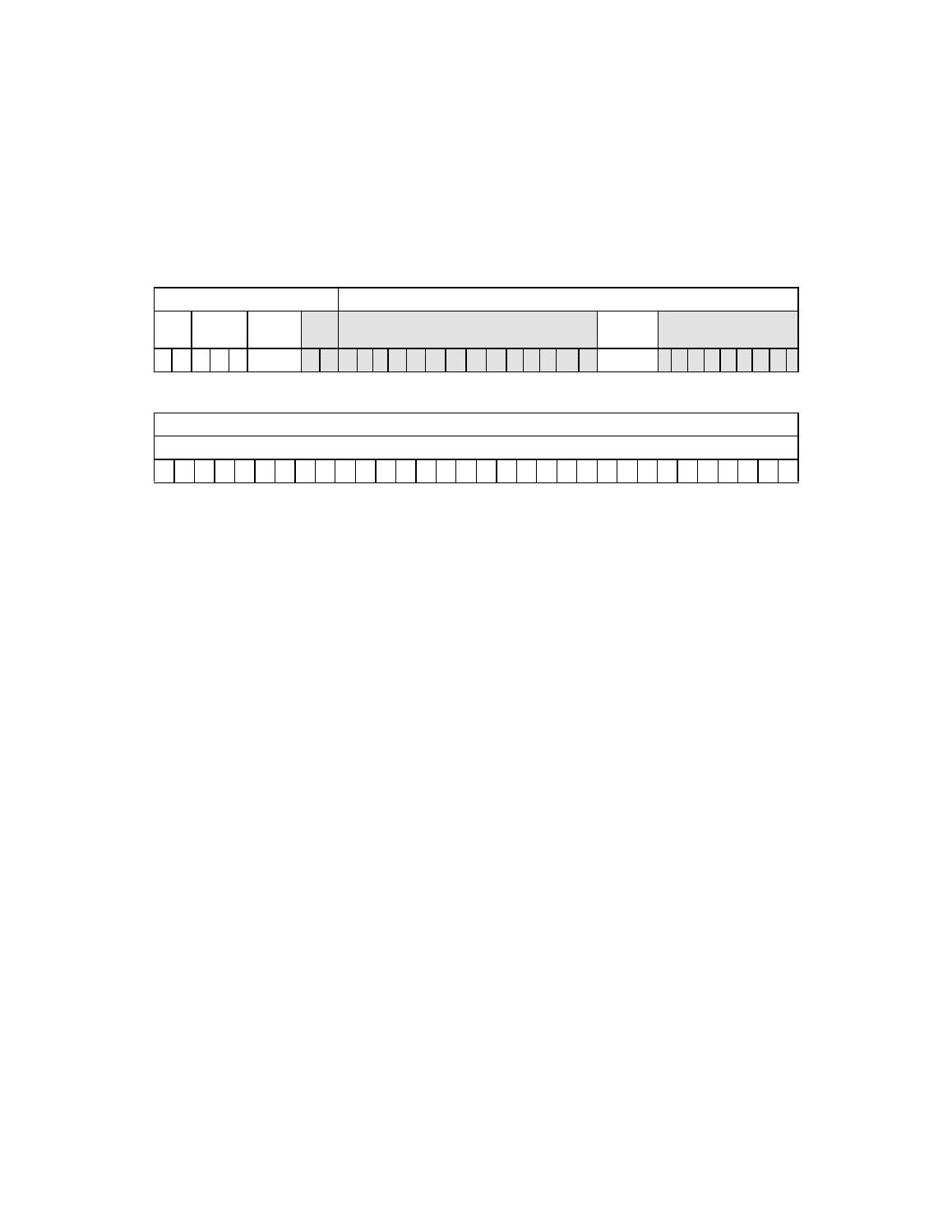

Figure 3.22 WAIT SELECT Format

31 30 29

27

26

25 24 23

10

9

8

0

DCMD Register

DBC Register

Instr

Type

Opcode

Relative

Mode

R

R

Set Target

Role

R

0

1

0

1

0

x

0

0

0 0 0 0

0

0

0

0

0

0 0 0

0

0

1

0 0 0 0 0 0 0 0 0

31

0

DSPS Register

Destination Address

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

Instruction

Type

I/O.

Opcode

Wait Select instruction.

Relative

Mode

Indicates that the 24-bit address is an offset from the current

program counter.

Set Target

Role

1 - places the chip into target mode

0 - places the chip into initiator mode

Destination

Address

Specifies the memory address to fetch the next instruction if

the device is reselected during the selection attempt, or if the

SIGP bit is set.