Table 6.3 scripts registers, 5 64-bit scripts selector registers, Table 6.4 64-bit selector registers – Avago Technologies LSI53C1010 User Manual

Page 156: Bit scripts selector registers, Scripts registers, Bit selector registers

6-6

Using the Registers to Control Chip Operations

registers are listed in

. They are described in

6.5 64-Bit SCRIPTS Selector Registers

lists the 64-bit Selector registers. The 64-bit Selector registers

reflect/control various aspects of 64-bit operation.

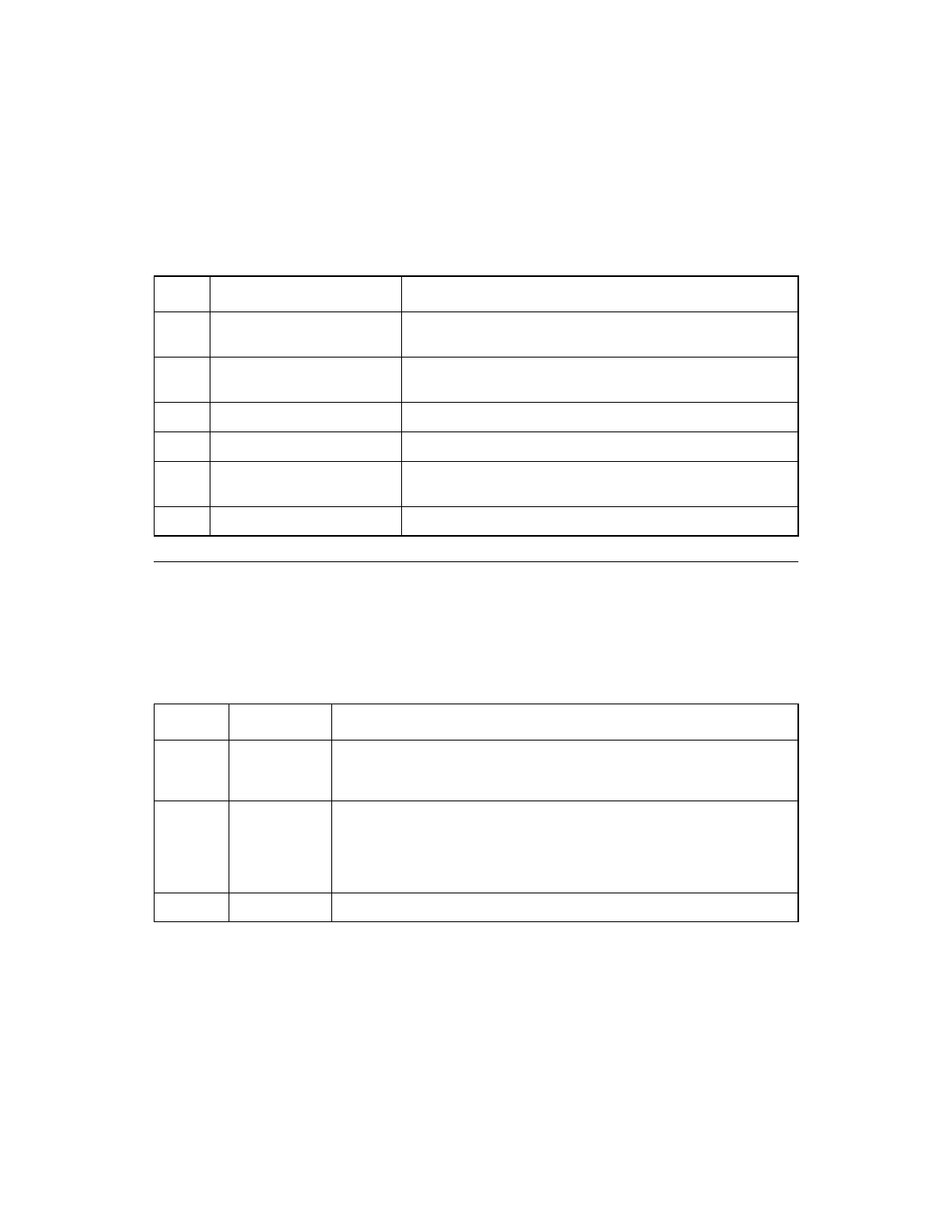

Table 6.3

SCRIPTS Registers

Name

Definition

Functions

DBC

DMA Byte Counter

Determines the number of bytes to be transferred in a Block

Move instruction.

DCMD

DMA Command

Identifies the instruction that the SCRIPTS processor will

execute.

DNAD

DMA Next Address

Contains the general purpose address pointer.

DSA

Data Structure Address

Contains base address used for all table indirect calculations.

DSP

DMA SCRIPTS Pointer

Contains the address of the next SCRIPTS instruction to be

fetched; placing an address in this register starts SCRIPTS.

DSPS

DMA SCRIPTS Pointer Save Contains the second Dword of a SCRIPTS instruction.

Table 6.4

64-Bit Selector Registers

Name

Definition

Functions

CCNTL0

1

Chip Control 0 Various JUMP control functions, Disable Auto-FIFO Clear, Disable

Internal Load/Store (LSI53C89X only), Disable Internal SCRIPTS RAM

Cycles (LSI53C10XX only), Disable Pipe Request

CCNTL1

1

Chip Control 1 Disable DAC, 64-bit Table Indirect Indexing Mode, Enable 64-bit Table

Indirect BMOV, Enable 64-bit Direct BMOV

LSI53C89X only: High Impedance Mode

LSI53C10XX only: Pull Enable, Pull Disable, Disable 64-bit Master

Operation, Disable 64-bit Slave Cycles

CCNTL2

2

Chip Control 2 Reserved