Table 8.1 data structure, 2 select/reselect instructions, Table 8.2 i/o data structure – Avago Technologies LSI53C1010 User Manual

Page 195: Select/reselect instructions, Data structure, I/o data structure

Table Indirect Addressing

8-9

8.6.2 Select/Reselect Instructions

During a Select/Reselect and when FROM is used to indicate table

indirect addressing, the 24-bit signed value in the DBC register is an

offset relative to the value of the DSA register. The table indirect feature

allows fetching the Synchronous Clock Conversion, Enable Wide SCSI,

Clock Conversion Factor, SCSI Device ID, Synchronous Offset, and

Synchronous Period bit values from an I/O data structure that is built at

the start of an I/O. Thus, an I/O can begin with no requirement to write

the values into the chip or into the actual SCRIPTS instruction in

memory. In the I/O data structure, the user must have written the

following 8-byte value, as shown in

.

The configuration information in byte lane 3 is mapped into the SCNTL3

register (0x03). This includes the Synchronous Clock Conversion Factor,

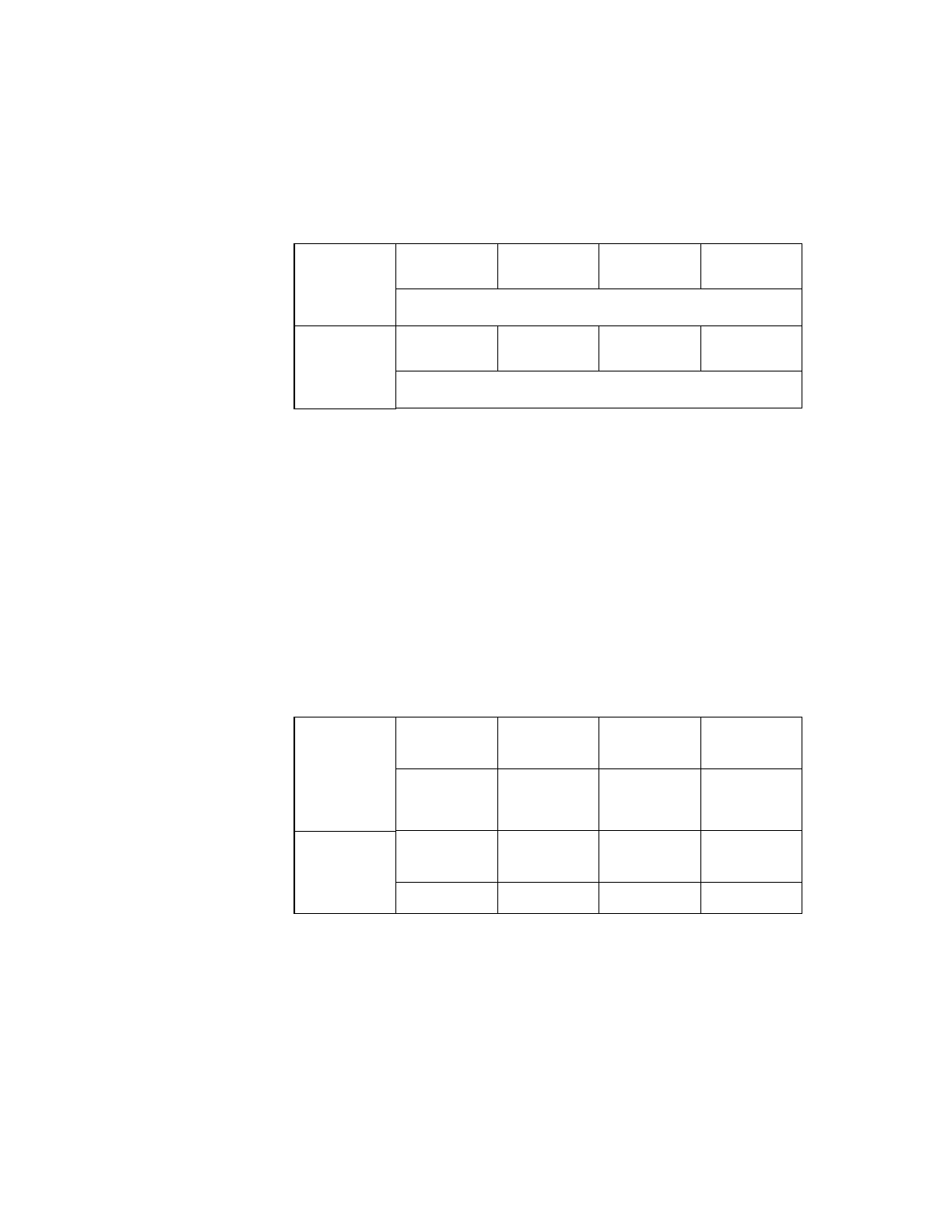

Table 8.1

Data Structure

Dword 0

Byte

Lane 3

Byte

Lane 2

Byte

Lane 1

Byte

Lane 0

Byte Count

Dword 1

Byte

Lane 3

Byte

Lane 2

Byte

Lane 1

Byte

Lane 0

Address

Table 8.2

I/O Data Structure

Dword 0

Byte

Lane 3

Byte

Lane 2

Byte

Lane 1

Byte

Lane 0

Config

(SCNTL3)

Device ID

(SDID)

Period &

Offset

(SXFER)

R

1

(SCNTL4)

2

1. LSI53C896 and earlier.

2. LSI53C10XX.

Dword 1

Byte

Lane 3

Byte

Lane 2

Byte

Lane 1

Byte

Lane 0

R

R

R

R