Avago Technologies LSI53C1010 User Manual

Page 53

Instruction Descriptions

3-13

Register

Definition(s)

The information listed below describes the DBC and DSPS registers:

Description

There are various forms of the Chained Block Move instruction. The

“address” and “count” specify the address and byte count fields of the

instruction. If the optional keyword “PTR” is present, the indirect bit is set.

If PTR is present, the address specified in the instruction is the address

of the pointer to the data in memory. “Phase” specifies the phase field of

the instruction. WITH or WHEN specify the Block Move function codes.

WITH signals the target role which sets the phase values, and WHEN is

the initiator “test for phase” feature.

The SCRIPTS processor waits for a valid phase (initiator) or drives the

phase lines (target). In the initiator role, it performs a comparison looking

for a match between the phase specified in the SCRIPTS instruction and

the actual value on the bus. If the phases do not match, an external

interrupt occurs. A test prior to the Move instruction could be used to

avoid this interrupt. If the phase does match, data is then transferred in

or out according to the phase lines. When the count goes to zero, the

SCRIPTS processor fetches the next sequential SCRIPTS instruction.

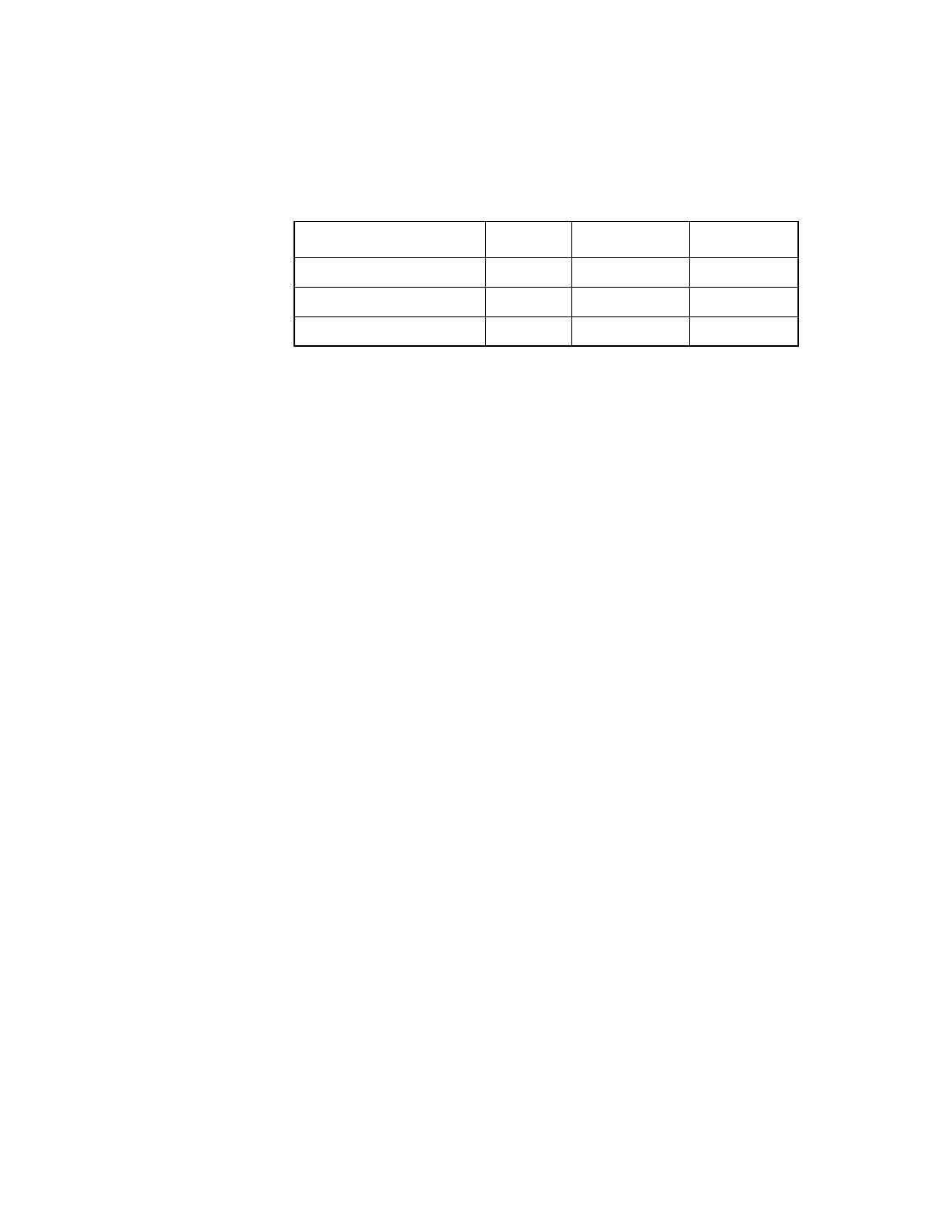

R5

4

(DT_DATA_IN

)3

1

0

1

MESSAGE_OUT

1

1

0

MESSAGE_IN

1

1

1

1. 0 - False, negated; 1 - True, asserted. For these phases, SEL is negated and

BSY is asserted.

2. All chips except LSI53C10XX.

3. LSI53C10XX chips.

4. RES4 and RES5 are reserved SCSI phases except in the LSI53C10XX chips.

Table 3.5

SCSI Phase Bit Values (CHMOV Format)

1

(Cont.)

Phase

Message

Command/Data

Input/Output

SCSI Phase

These bits reflect the actual values of the SCSI phase lines.

Byte Count

A 24-bit number indicating the number of bytes to transfer.

Dest Addr

Address to perform data transfer on, or offset from the DSA to

fetch table indirect information.