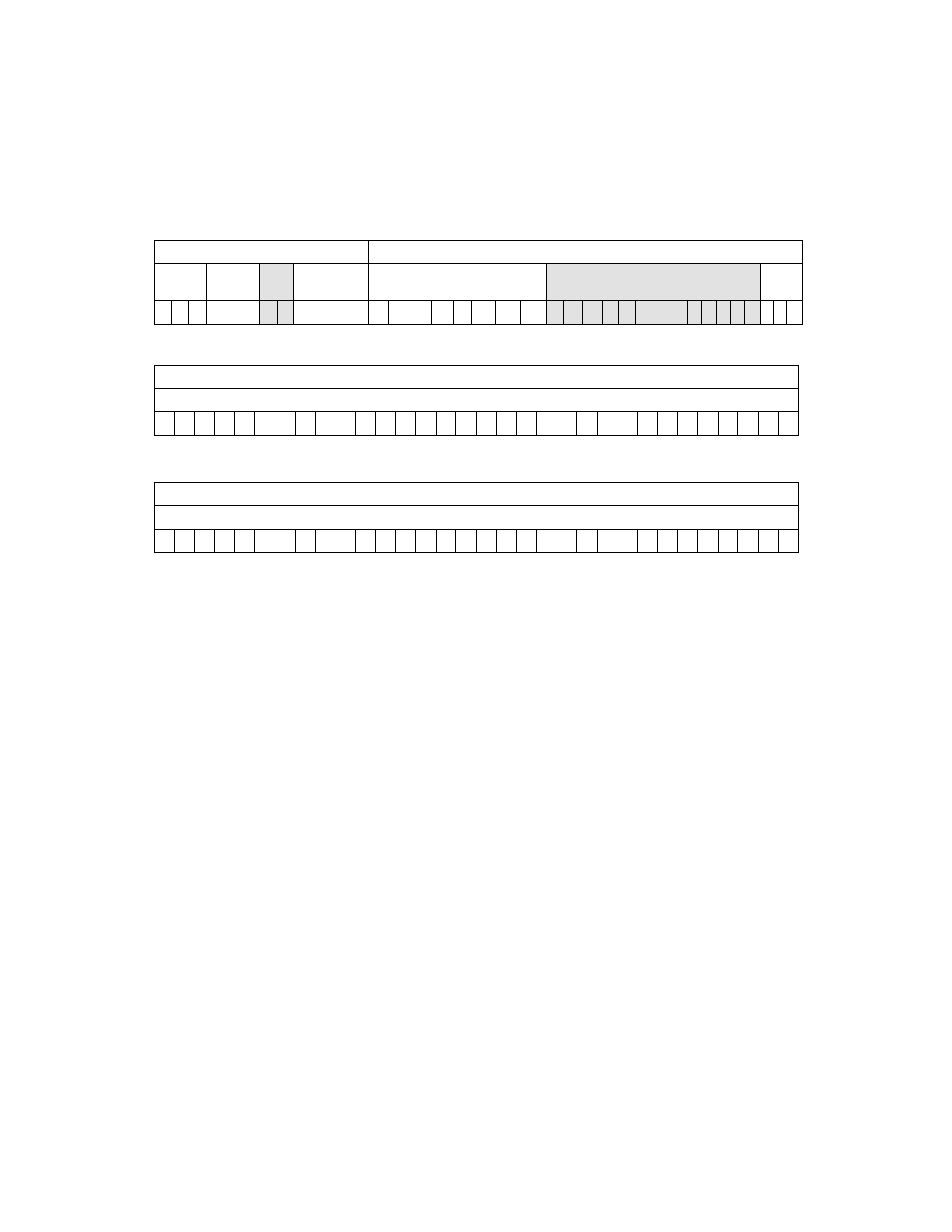

Table 3.11 load64 format, Load64 format – Avago Technologies LSI53C1010 User Manual

Page 81

Instruction Descriptions

3-41

Field(s)

This command has the following fields:

Table 3.11

LOAD64 Format

31 30 29

28

27 26

25

24

23 22 21 20 19 18 17

16 15

8 7

3 2

0

DCMD Register

DBC Register

Instr

Type

DSA

Relative

R

No

Flush

Load/

Store

Register Address

R

Byte

Count

1 1 1

x

0 0

x

1

A7 A6 A5 A4 A3 A2 A1 A0 0 0

0 0 0 0 0 0 0 0 0 0 0 x x x

31

0

DSPS Register

Source Address/DSA Offset

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

31

0

MMRS Register

Destination Address

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

Instruction

Type

Load/Store.

DSA Relative

Indicates source address location.

0 - DSPS contains actual address of data to load.

1 - DSPS contains a 24-bit offset value that is added to the

DSA to determine the source address.

No Flush

Indicates a store instruction without flushing the prefetch unit.

The Pre-fetch Enable bit in the DMA Control (DCNTL) register

must be set.

Load/Store

This field defines whether the instruction will be executed as a

Load or a Store.

0 - Store instruction

1 - Load instruction

Register

Address

These bits select the register to load within the chip operating

register set.

Byte Count

Indicates the number of bytes to transfer. Valid values are 1,

2, 3, or 4.

Source

Address

Actual Address (or offset from the DSA) of the data to load into

the chip register.