6 table indirect block move summary, 7 lsi53c1010/lsi53c1010r, Table indirect block move summary – Avago Technologies LSI53C1010 User Manual

Page 280: Lsi53c1010/lsi53c1010r

13-10

New SCRIPTS Processor Features

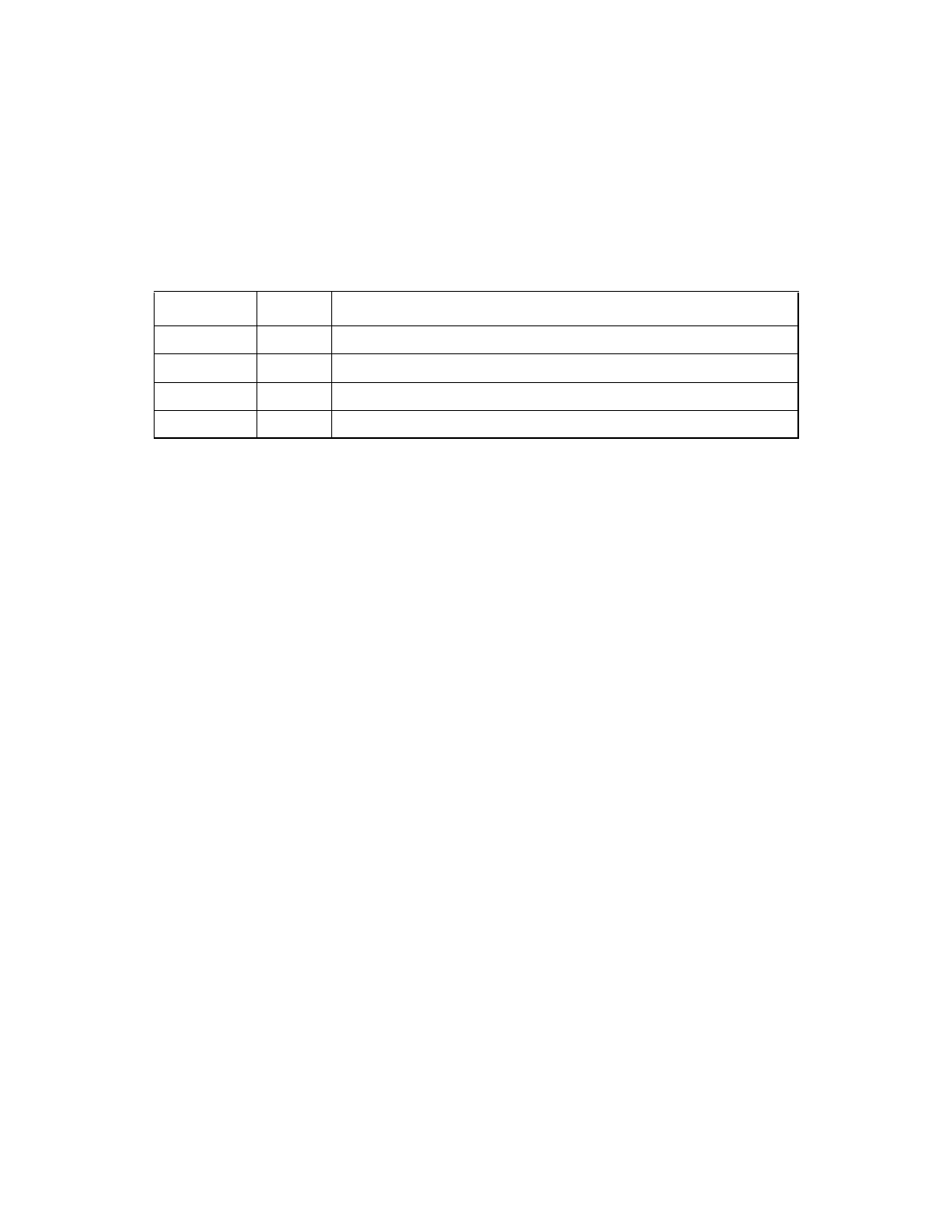

13.7.6 Table Indirect Block Move Summary

summarizes the address locations for a table indirect move.

13.7.7 LSI53C1010/LSI53C1010R

This chip supports Ultra3 SCSI, which is enabled in SCNTL4. It uses DT

timing. It also has two new SCSI phases.

•

DT_DATA_OUT

•

DT_DATA_IN

The chip also supports Byte Recovery and shadowed registers SIST0

and SIST1. Specifics for these registers are listed below.

•

SIST0

Pad Request with no CRC Request Following

Force CRC

Switch from DT to ST timings during a transfer

Phase Change with no final CRC Request

Multiple CRC Requests with the same offset

•

SIST1

Residual Data in SCSI FIFO

Phase Change with outstanding Offset

Offset Overflow

Offset Underflow

Data Overflow

Data Underflow

Table 13.3

Table Indirect BMOV Upper 32-Bit Address Locations

EN64TIBMOV

64TIMOD

Upper 32-bit Address Source

0

0

SBMS

0

1

SBMS

1

0

ScratchC–R, MMWS, MMRS, SPS, DRS, DBMS

1

1

First table entry Dword bits 31–24 (40-bit addressing)