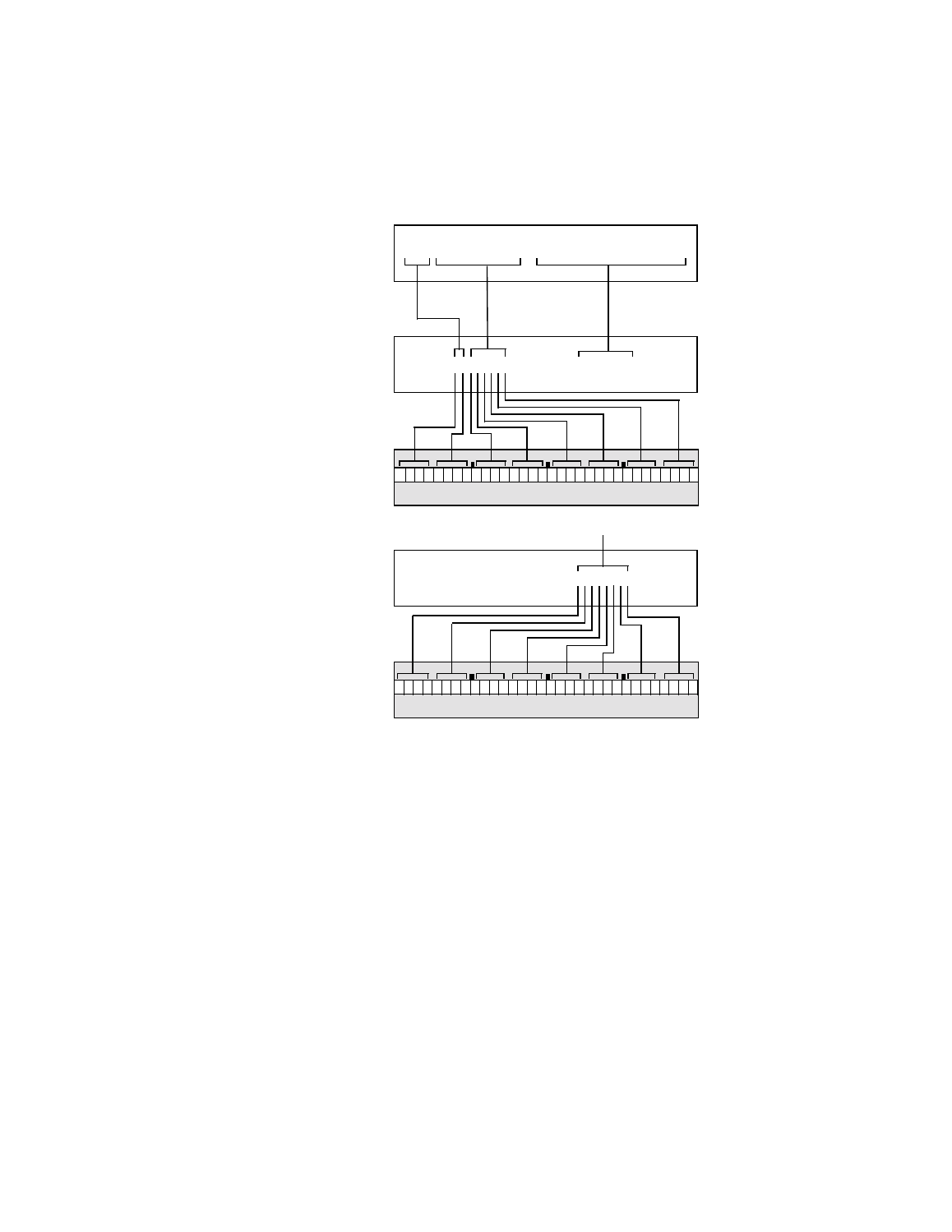

Figure3.30 block move instruction, 6 load/store instruction example, Load/store instruction example – Avago Technologies LSI53C1010 User Manual

Page 119: Block move instruction, Figure 3.30 block move instruction

Instruction Examples

3-79

Figure 3.30 Block Move Instruction

3.3.6 Load/Store Instruction Example

In this example, shown in

, the processor waits for a valid

phase, indicated by assertion of SREQ/, and compares it to the CMD

phase. If the phase matches, the processor then transfers the CDB from

the address represented by the

command_buffer

. In the hexadecimal

version of the first 32-bit word of the instruction, STORE with the No

Flush option is represented by E2, which translates into binary as an

opcode of 111, indicating a Load/Store instruction type. The 0 indicates

that the DSPS value is the actual address to STORE from, and 0b0010

indicates that the prefetch buffer will not be flushed during the STORE,

and that the SCRIPTS processor is performing a STORE rather than a

NASM

Output

Binary

Instruction

Format

0

0 0 1 0 1

0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0

0

0

0

DCMD Register

DBC Register

0A000006

00000012

SCSI SCRIPTS

Source Code

0

0 0 0 0 0

0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0

0

0

0

DSPS Register

Binary

Instruction

Format

0A000006

00000012

(

command_buffer

)

NASM

Output

MOVE command_length, command_buffer, WHEN CMD