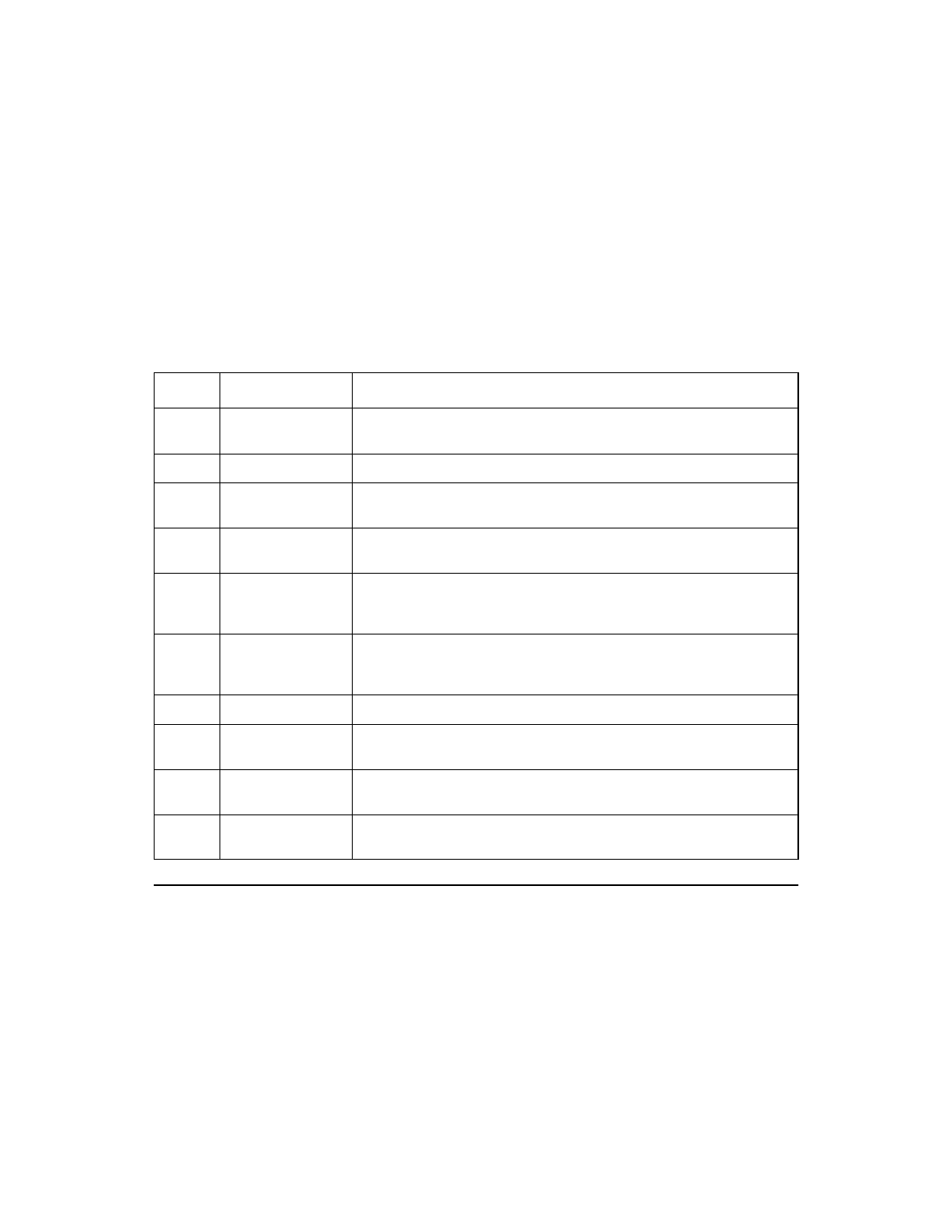

Table 6.2 dma registers, 4 scripts registers, Scripts registers – Avago Technologies LSI53C1010 User Manual

Page 155: Dma registers

SCRIPTS Registers

6-5

•

Obtaining DMA interrupt status information contained in the DMA

Status (DSTAT) register.

•

Obtaining DMA FIFO information, such as the number of bytes it

contains.

•

Enabling or masking DMA interrupts with the DMA Interrupt Enable

(DIEN) registers.

6.4 SCRIPTS Registers

The SCRIPTS registers hold the SCRIPTS instruction information which

is fetched from host memory at run time by the SCRIPTS processor.

MBOX registers are also used as SCRIPTS registers. The SCRIPTS

Table 6.2

DMA Registers

Name

Definition

Functions

DBC

DMA Byte Counter

Determines the number of bytes to be transferred in a Block Move

instruction.

DCMD

DMA Command

Identifies the instruction that the chip will execute.

DCNTL

DMA Control

Enables the Single Step Mode; LSI53C700 compatibility bit; enables

the PCI Cache Line Size register; enables instruction prefetching.

DFIFO

DMA FIFO

May be used to determine the number of bytes in the DMA FIFO

when an interrupt occurs, when used in conjunction with DBC.

DIEN

DMA Interrupt

Enable

Contains interrupt mask bits corresponding to master data parity

error, bus fault, aborted, single step interrupt, SCRIPT interrupt

instruction received, illegal instruction detected

DMODE

DMA Mode

Defines burst length; near or far memory access; enables PCI read

line command; Manual Start Mode bit to prevent automatic execution

of SCRIPTS.

DNAD

DMA Next Address Contains the general purpose address pointer.

DSP

DMA SCRIPTS

Pointer

Contains the address of the next SCRIPTS instruction to be fetched.

Placing an address in this register starts SCRIPTS.

DSPS

DMA SCRIPTS

Pointer Save

Contains the second Dword of a SCRIPTS instruction.

TEMP

Temporary

Register

Stores pointer to the next SCRIPTS instruction to be executed when

returning from a subroutine.