4 read/write instructions, Table 3.2 read/write instructions, 5 block move instructions – Avago Technologies LSI53C1010 User Manual

Page 43: 6 load and store instructions, Read/write instructions, Block move instructions, Load and store instructions

Overview of SCRIPTS Instructions

3-3

bit, and may enable interrupt on the fly, so that the interrupt instruction

does not halt the SCRIPTS processor.

3.1.4 Read/Write Instructions

The Read/Write Instruction type is selected when the two high order bits

of the DCMD register are 0b01, with the opcode bit values from

0b101–0b111. Read/Write instructions perform the following register

operations, depending on the value of the operator bits in the Move

Register instructions.

describes these instructions.

3.1.5 Block Move Instructions

The Block Move instruction type is selected when the two high order bits

of the DCMD register are 0b00. Block Moves transfer data (user data or

SCSI information) between user memory and the SCSI bus. Data comes

from any memory address, so scatter/gather operations for user data are

transparent to the chip and the external processor. A separate Block

Move instruction is written for each piece of data being moved. This

instruction allows indirect and table indirect addressing.

3.1.6 Load and Store Instructions

The Load/Store instruction type is selected when the three high order

bits of the DCMD register are 0b111. Load and Store instructions are a

more efficient way to move data directly between memory and an internal

register than the Memory Move instruction. This is due to the fact that

they utilize two Dwords instead of three and require one PCI bus

ownership instead of two. Load and Store instructions move a maximum

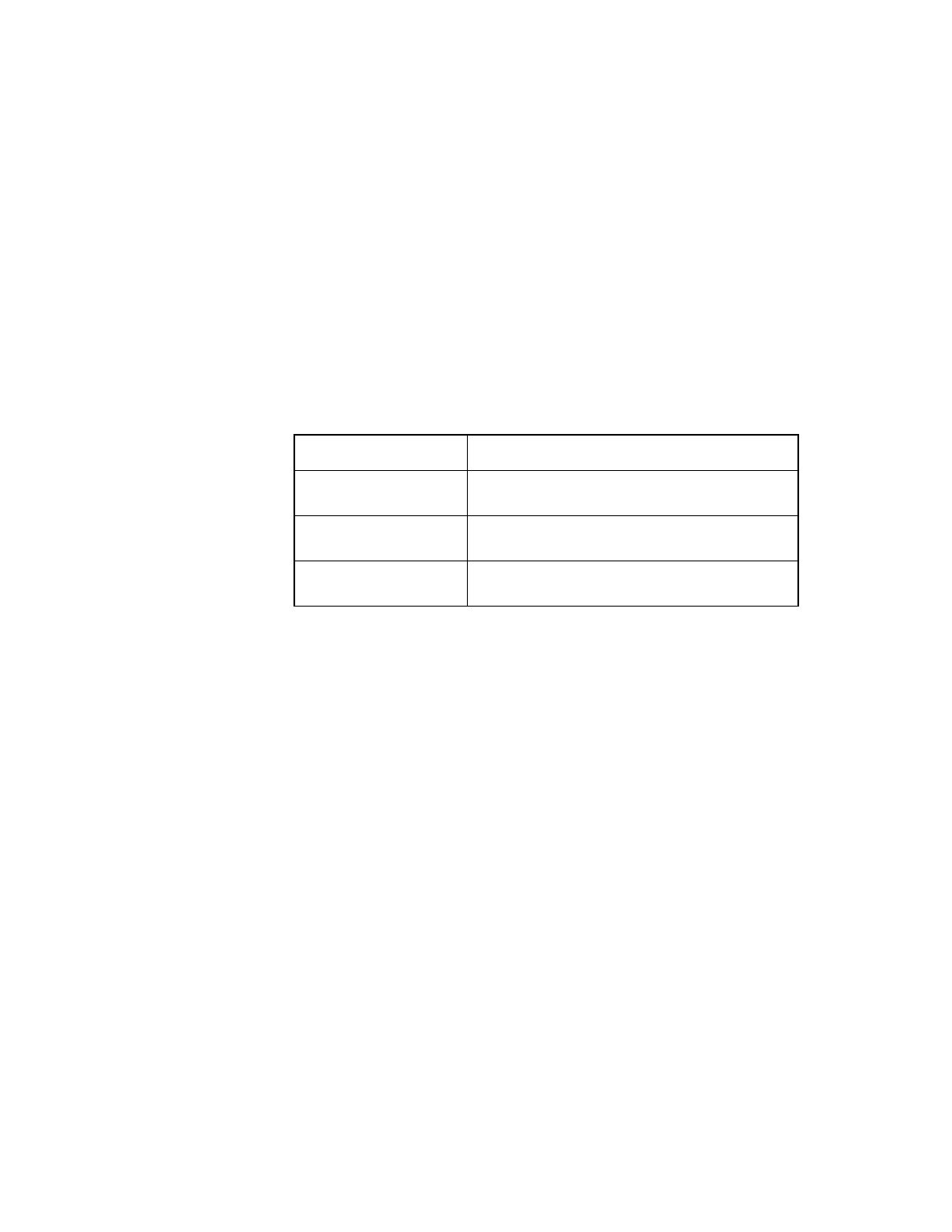

Table 3.2

Read/Write Instructions

Instruction Type

Definition

Move from SFBR

Moves the SCSI First Byte Received (SFBR)

register (0x08) to a specified register address.

Move to SFBR

Moves a specified register value to the SFBR

register.

Read/Modify/Write

Reads a specified register, modifies it, and writes

the result back into the same register.