Avago Technologies LSI53C1010 User Manual

Page 59

Instruction Descriptions

3-19

Field(s)

This command has the following fields:

Register

Definition(s)

The information listed below describes the DBC and DSPS registers:

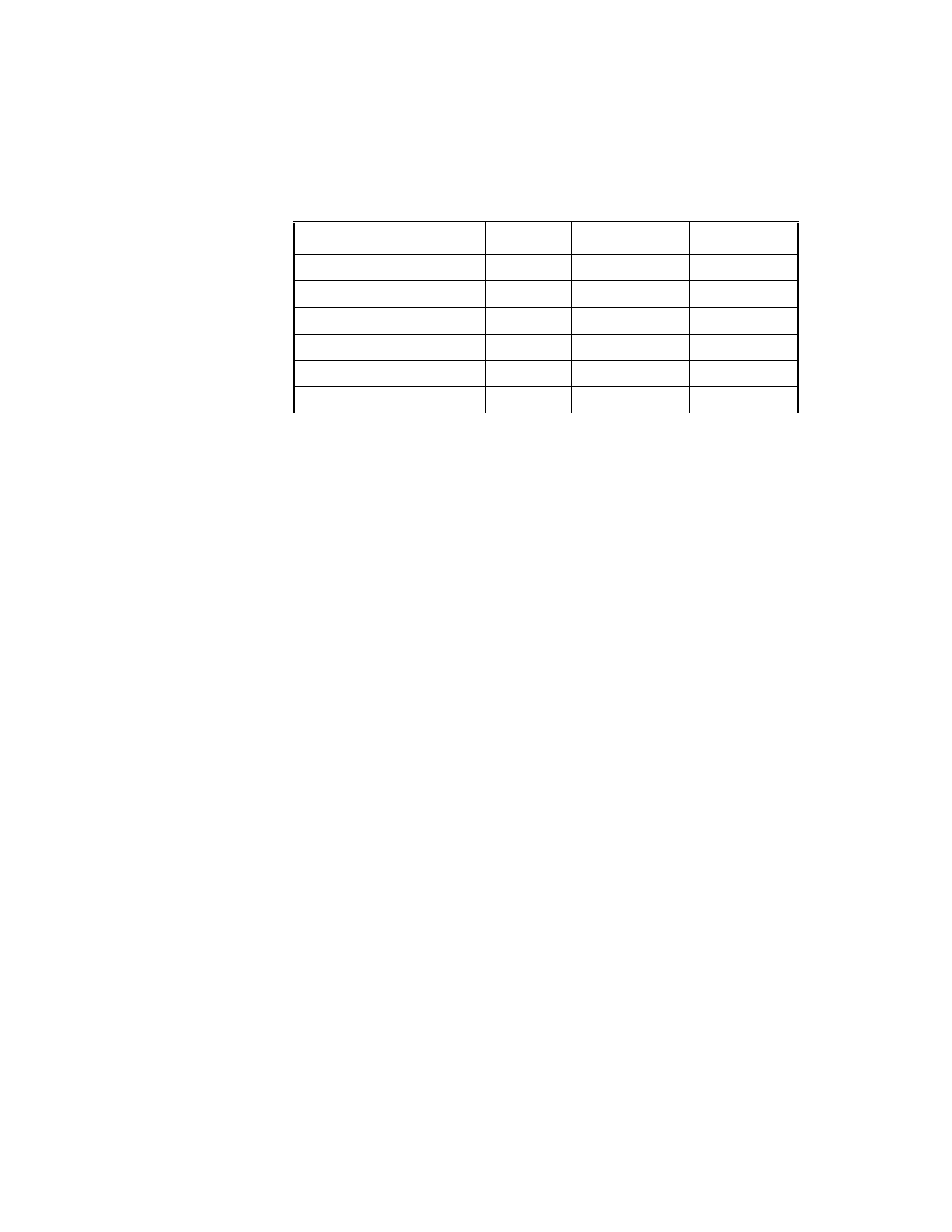

COMMAND

0

1

0

STATUS

0

1

1

RES4

4

(DT_DATA_OUT)

3

1

0

0

RES5

4

(DT_DATA_IN

)3

1

0

1

MESSAGE_OUT

1

1

0

MESSAGE_IN

1

1

1

1. 0 - False, negated; 1 - True, asserted. For these phases, SEL is negated and

BSY is asserted.

2. All chips except LSI53C10XX.

3. LSI53C10XX chips.

4. RES4 and RES5 are reserved SCSI phases except in the LSI53C10XX chips.

Table 3.6

SCSI Phase Bit Values (INT Format) (Cont.)

1

Phase

Message

Command/Data

Input/Output

Instruction

Type

Transfer Control.

Opcode

Interrupt Instruction.

SCSI Phase

These bits reflect the actual values of the SCSI phase lines.

Carry Test

When this bit is set, true/false comparisons are based on the ALU

Carry bit. Carry comparisons cannot be made at the same time as

data and phase comparisons.

True

Transfer on TRUE/FALSE condition.

0 - Transfer if condition is FALSE

1 - Transfer if condition is TRUE

Compare

Data

Compare data byte to first byte of the received data.

0 - Do not compare data

1 - Perform comparison

Compare

Phase

Compare current SCSI phase to SCSI phase field or SATN/. This

bit is set whenever the Phase operand is used.

0 - Do not compare phase

1 - Perform comparison