Avago Technologies LSI53C1010 User Manual

Page 153

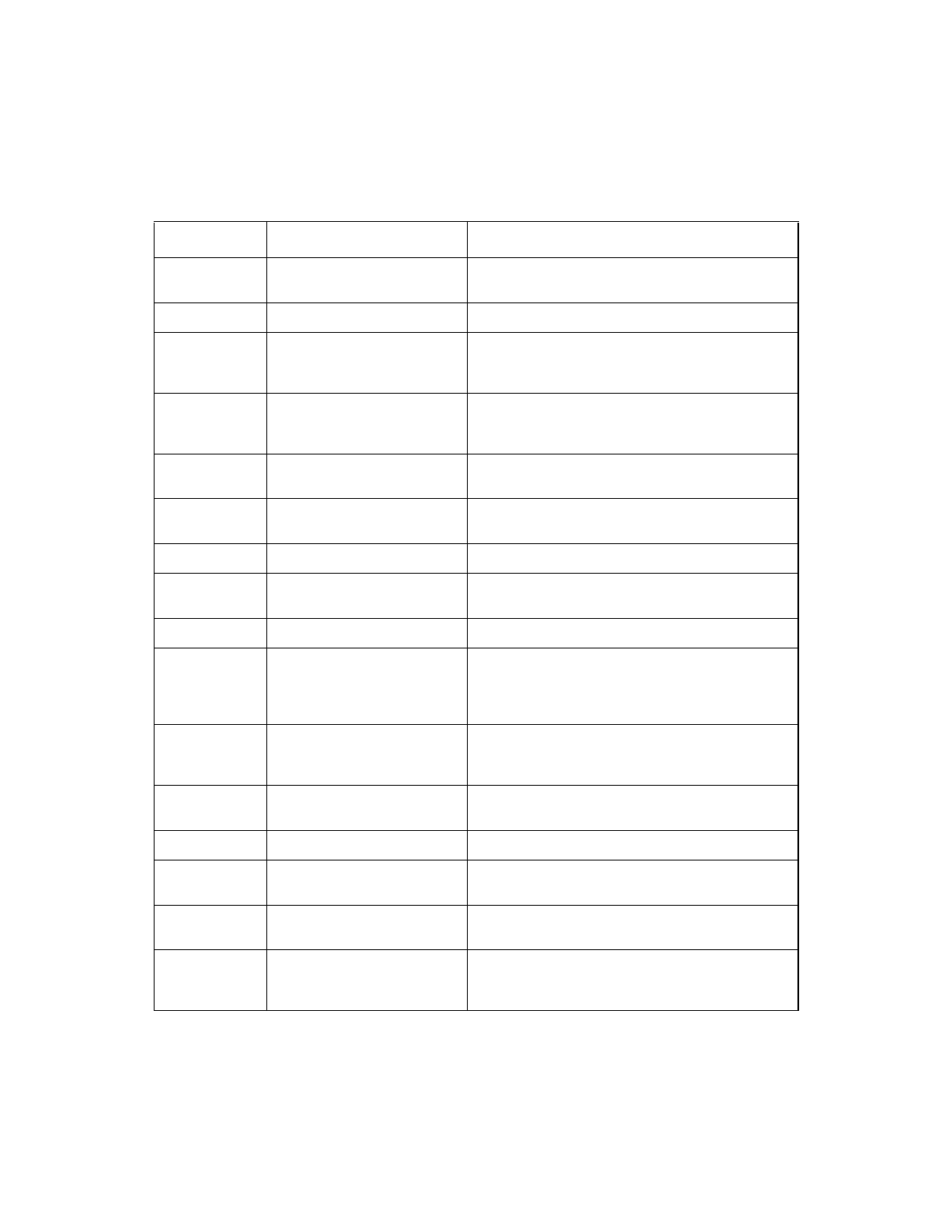

SCSI Registers

6-3

SCID

SCSI Chip ID

Enable response to selection/reselection, set SCSI

ID for chip.

SCNTL0

SCSI Control 0

Arbitration Mode bits; enable parity checking.

SCNTL1

SCSI Control 1

Add an extra clock cycle of setup to each SCSI

data transfer; disable halt on parity error;

Connected bit; parity bits; Immediate Arbitration bit.

SCNTL2

SCSI Control 2

Wide SCSI control bits, vendor unique

enhancements; DIFFSENS mismatch indicator

(LSI53C895 only).

SCNTL3

SCSI Control 3

Clock conversion factor bits, enable wide SCSI,

enable Ultra SCSI or Ultra2 SCSI.

SCNTL4

2

SCSI Control 4

This register is used during Table Indirect Select or

Reselect SCRIPTS instructions.

SDID

SCSI Destination ID

Encoded destination SCSI ID.

SFBR

SCSI First Byte Received

Contains the first byte received in any

asynchronous information transfer phase.

SIDL

SCSI Input Data Latch

Contains latched data from the SCSI bus.

SIEN0

SCSI Interrupt Enable 0

Interrupt mask bits for phase mismatch, SATN/,

function complete, selection/reselection, gross

error, unexpected disconnect, SCSI reset, parity

error.

SIEN1

SCSI Interrupt Enable 1

Interrupt mask bits for selection/reselection

time out, general purpose time-out, handshake-to-

handshake time-out.

SLPAR

SCSI Longitudinal Parity

Performs a bytewise longitudinal parity check on all

SCSI data.

SOCL

SCSI Output Control Latch

Testing SCSI control lines.

SODL

SCSI Output Data Latch

Data flows through this register when sending data

in any mode.

SSID

SCSI Selector ID

The ID of the device that selected or reselected the

chip.

SSTAT0

SCSI Status 0

SIDL, SODR, SODL least significant byte full;

arbitration reporting bits; status of RST/ and SDP0/

signals.

Table 6.1

SCSI Registers (Cont.)

Name

Definition

Functions