Set_enable_a_begintransfer_exist(), Set_enable_a_begintransfer_legal(), Set_enable_a_begintransfer_single_cycle() – Altera Avalon Verification IP Suite User Manual

Page 78

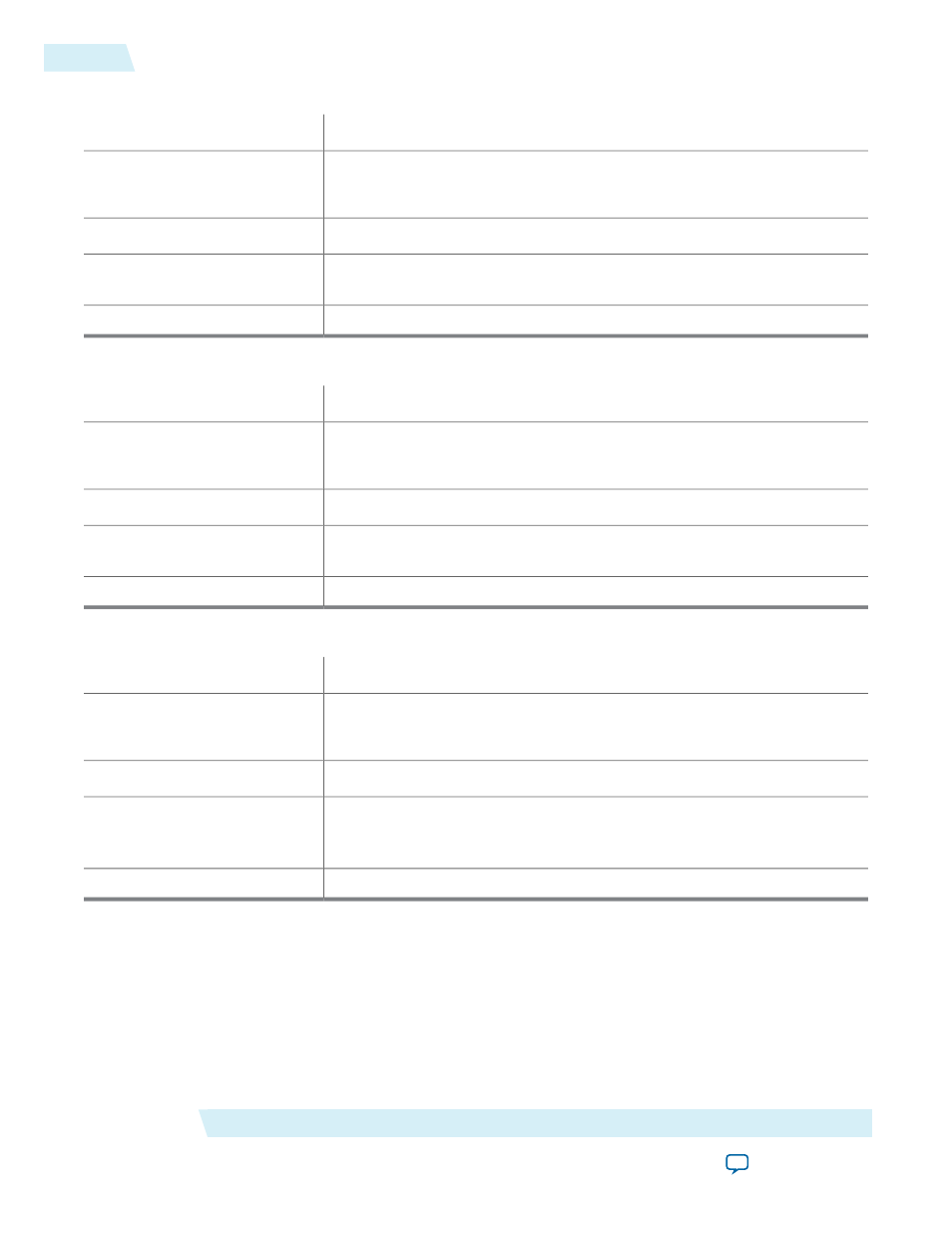

set_enable_a_begintransfer_exist()

set_enable_a_begintransfer_exist()

Prototype:

Verilog HDL:

Boolean

VHDL: N.A.

Arguments:

void

Returns:

Enables an assertion that ensures

begintransfer

is asserted during any

single transfer. Disabled when either

begintransfer

is not supported.

Description:

Verilog HDL

Language support:

set_enable_a_begintransfer_legal()

set_enable_a_begintransfer_legal()

Prototype:

Verilog HDL:

Boolean

VHDL: N.A.

Arguments:

void

Returns:

Enables an assertion that ensures

begintransfer

is asserted together with

either

read

or

write

. Disabled when either

begintransfer

is not supported.

Description:

Verilog HDL

Language support:

set_enable_a_begintransfer_single_cycle()

set_enable_a_begintransfer_single_cycle()

Prototype:

Verilog HDL:

Boolean

VHDL: N.A.

Arguments:

void

Returns:

Enables an assertion that ensures

begintransfer

is asserted for only 1 cycle

and not reasserted for any single transfer, regardless of the status of the

waitrequest

signal.

Description:

Verilog HDL

Language support:

Avalon-MM Monitor

Altera Corporation

set_enable_a_begintransfer_exist()

7-6