Signal_fatal_error, Signal_instructions_completed, Signal_instruction_start – Altera Avalon Verification IP Suite User Manual

Page 189: Signal_max_instruction_queue_size

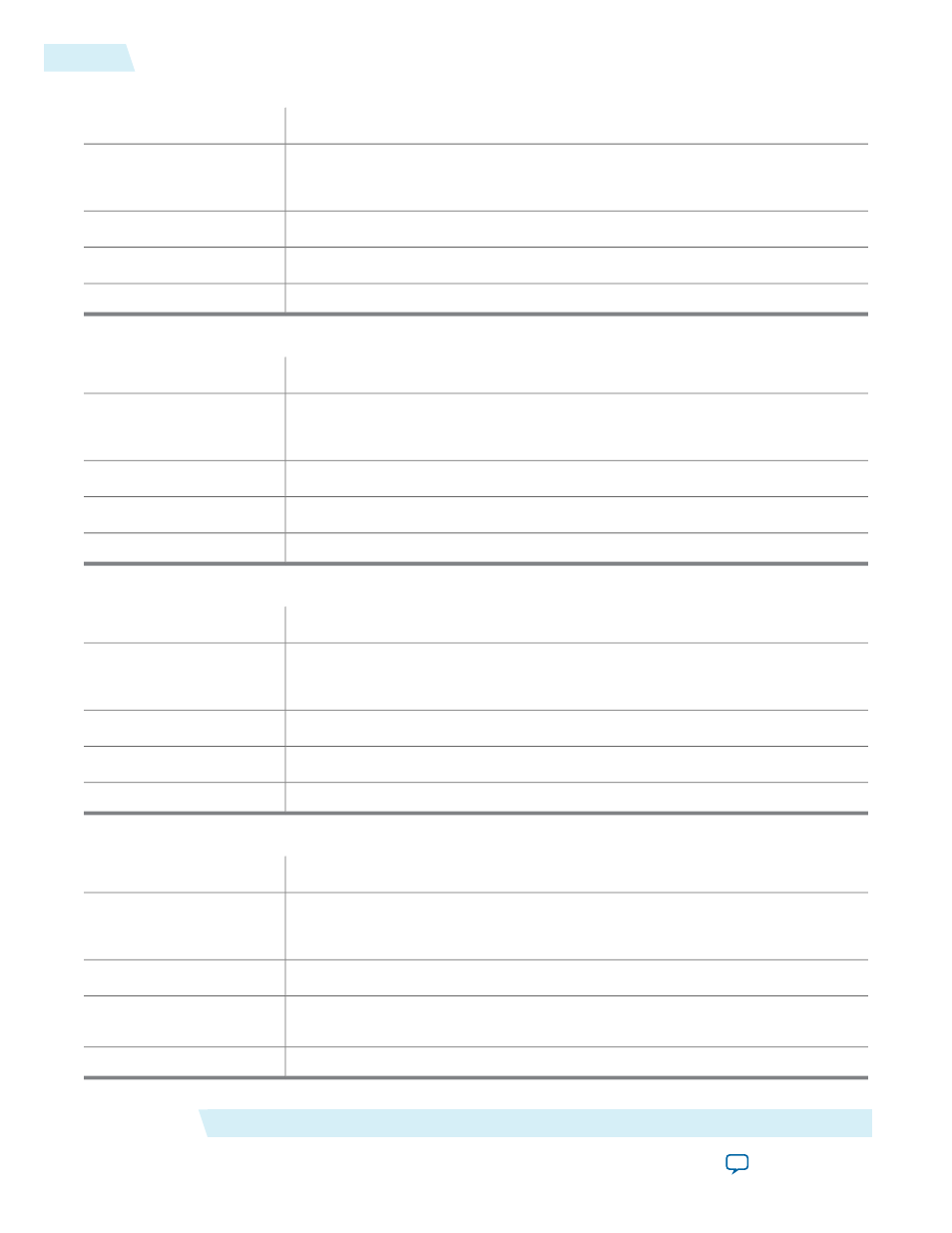

signal_fatal_error

signal_fatal_error

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void

Returns:

Notifies the testbench that a fatal error has occured in this module.

Description:

Verilog HDL

Language support:

signal_instructions_completed

signal_instructions_completed

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void

Returns:

Signals that all instructions in the BFM has been executed.

Description:

Verilog HDL

Language support:

signal_instruction_start

signal_instruction_start

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void

Returns:

Signals that an instruction has been driven to the interface.

Description:

Verilog HDL

Language support:

signal_max_instruction_queue_size

signal_max_instruction_queue_size

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void

Returns:

Signals that the maximum pending instruction queue size threshold has been

exceeded.

Description:

Verilog HDL

Language support:

Nios II Custom Instruction Master BFM

Altera Corporation

signal_fatal_error

14-14