Do run_simulation.tcl – Altera Avalon Verification IP Suite User Manual

Page 218

The Qsys Generate window displays informational messages as it generates the testbench.

d. Close the Generate window.

4. Start the ModelSim

®

simulator.

5. To run the simulation, type the following command in your working directory:

do run_simulation.tcl

This command compiles all the required HDL files, elaborates, and runs the simulation.

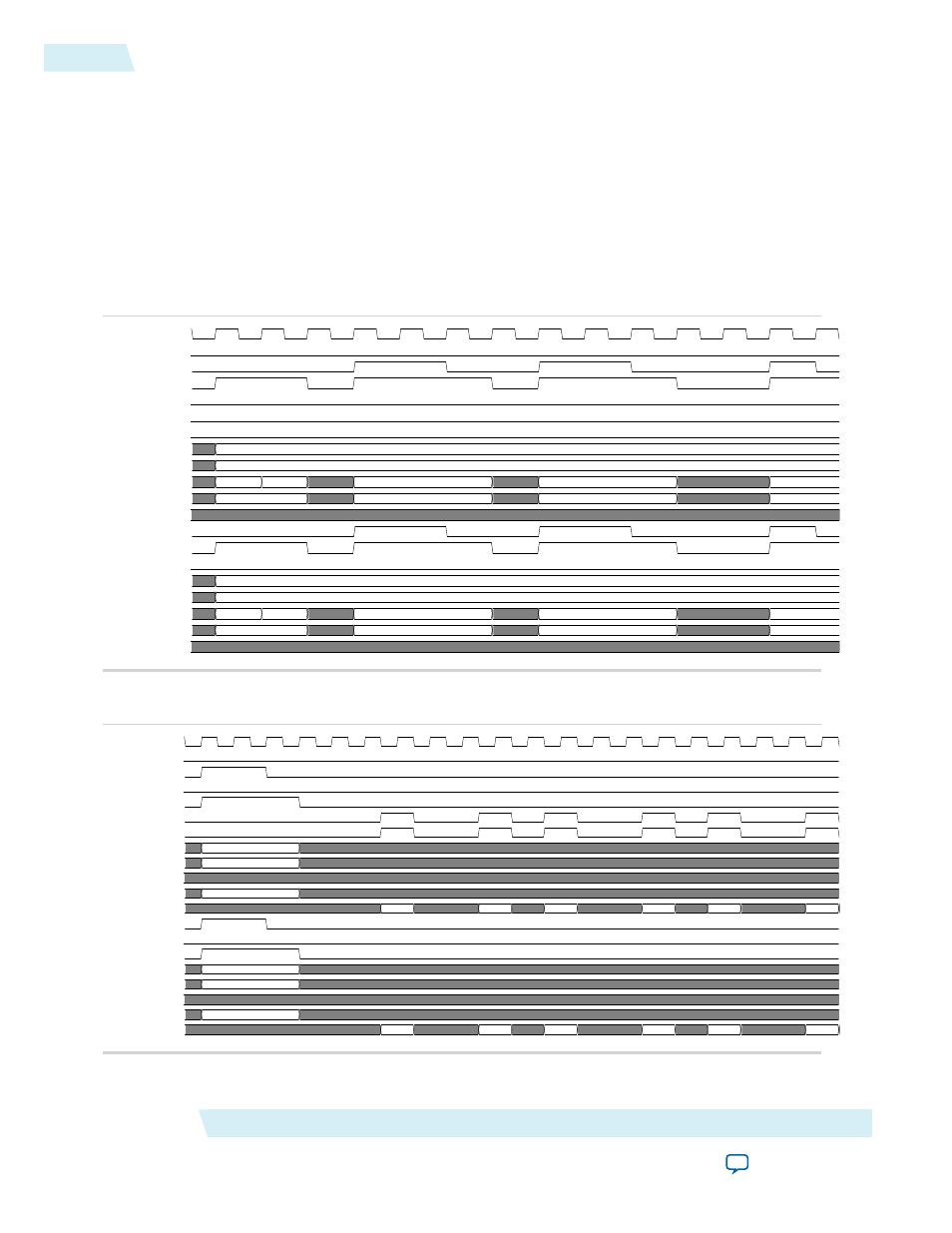

Figure 17-6: Timing for a Write Burst with a Burst Count of Five

tb.clk

tb.reset

mstr_0.avm_waitrequest

mstr_0.avm_write

mstr_0.avm_read

mstr_0.avm_readdatavalid

slv_0.avs_readdatavalid

mstr_0.avm_address[11:0]

mstr_0.avm_burstcount[3:0]

mstr_0.avm_writedata[31:0]

mstr_0.avm_byteenable[3:0]

mstr_0.avm_readdata[31:0]

slv_0.avs_waitrequest

slv_0.avs_write

slv_0.avs_read

slv_0.avs_address[11:0]

slv_0.avs_burstcount[3:0]

slv_0.avs_writedata[31:0]

slv_0.avs_byteenable[3:0]

slv_0.avs_readdata[31:0]

B2F

5

0000000D

00000003

00000016

0000000D

0000000B

F

F

F

F

B2F

5

0000000D

00000003

00000016

0000000D

0000000B

F

F

F

F

Figure 17-7: Timing for a Read with a Burst Count of Six

tbclk

tbreset

mstr_0avm_waitrequest

mstr_0avm_write

mstr_0avm_read

mstr_0avm_readdatavalid

slv_0avs_readdatavalid

mstr_0avm_address[11:0]

mstr_0avm_burstcount[3:0]

mstr_0avm_writedata[31:0]

mstr_0avm_byteenable[3:0]

mstr_0avm_readdata[31:0]

slv_0avs_waitrequest

slv_0avs_write

slv_0avs_read

slv_0avs_address[11:0]

slv_0avs_burstcount[3:0]

slv_0avs_writedata[31:0]

slv_0avs_byteenable[3:0]

slv_0avs_readdata[31:0]

A6F

6

F

0000000E

00000010

00000004

00000007

00000015

0000001A

A6F

6

F

0000000E

00000010

00000004

00000007

00000015

000000A

Avalon-MM Verilog HDL and VHDL Testbenches

Altera Corporation

Running the Testbench for a Single Avalon-MM Master and Slave Pair

17-8