Pair -2 – Altera Avalon Verification IP Suite User Manual

Page 212

The Slave Thread performs the following functions:

• Randomly sets backpressure cycles to Avalon-MM Slave BFM

• Waits for valid commands

• Retrieves valid commands from the Avalon-MM Slave BFM

• Verifies commands against the expected command

• Sends read data for read commands. The read data is saved in a FIFO for verification

The Master Response Thread performs the following functions:

• Waits for valid read data responses

• Retrieves read responses from the BFM

• Verifies the read response against the expected data

The test program sends the following transaction types:

• Non-bursting writes

• Non-bursting reads

• Bursting writes

• Bursting reads

Running the Verilog HDL Testbench for a Single Avalon-MM Master and Slave Pair

1. Unzip

ug_avalon_verification.zip

to a working directory.

2. Open

.

3. Complete the following steps to generate the testbench:

a. On the Generate menu, select Generate HDL.

b. Specify the parameters shown in the following table:

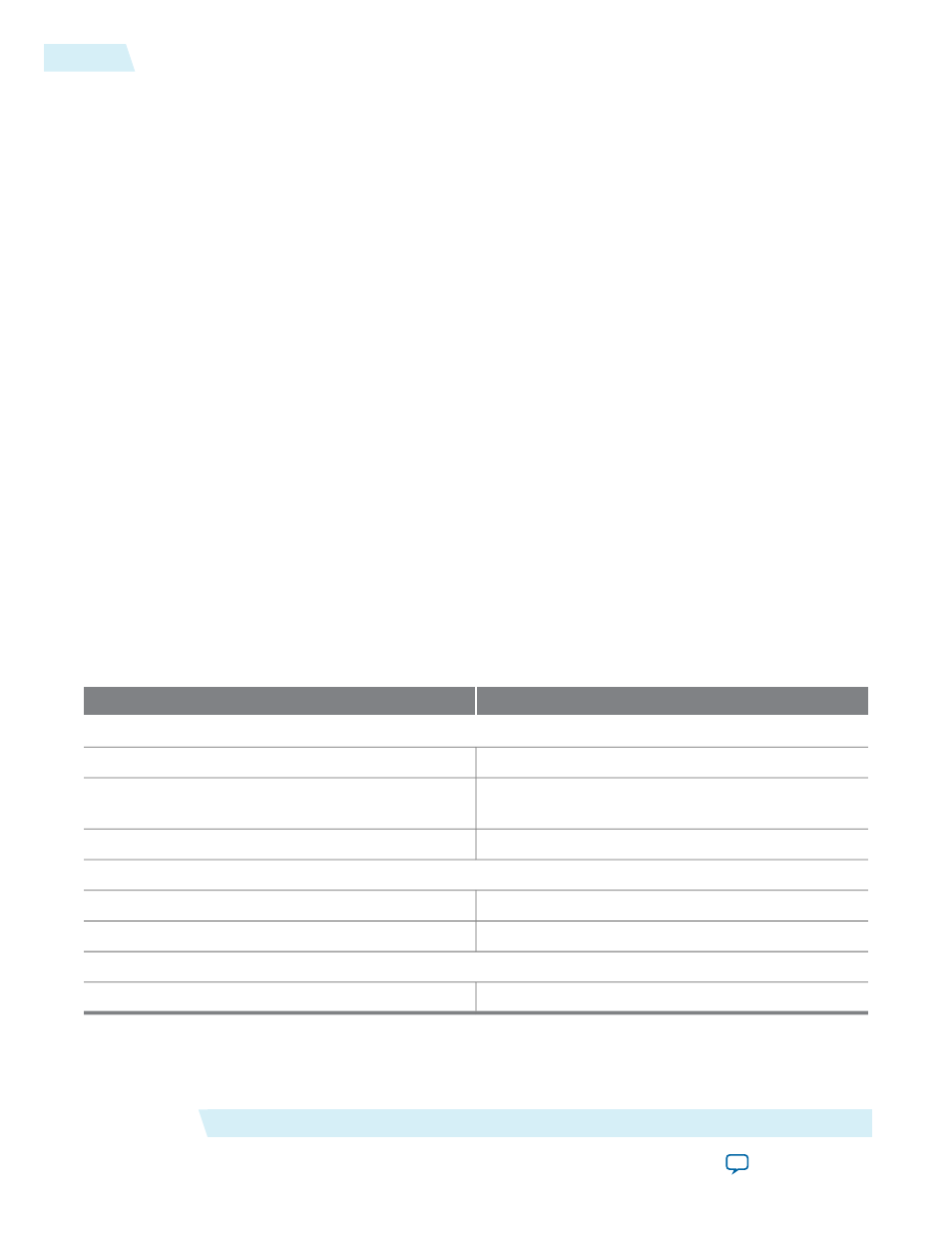

Table 17-1: Generation Parameters

Value

Parameter

Synthesis

Leave this option off

Create HDL design files for synthesis

Leave this option off

Create timing and resource estimates for third-party

EDA synthesis tools

Leave this option on

Create block symbol file (.bsf)

Simulation

Verilog

Create simulation model

Leave this option off

Allow mixed-language simulation

Output Directory

Path

c. Click Generate.

Avalon-MM Verilog HDL and VHDL Testbenches

Altera Corporation

Running the Verilog HDL Testbench for a Single Avalon-MM Master and Slave Pair

17-2