Setting up the test, Setting up the test -3 – Altera Avalon Verification IP Suite User Manual

Page 206

3. The parallel processes terminate when the Avalon-ST Source and Sink BFM transaction queues are empty

and all four transactions are complete.

4. The test program prints a pass or fail message in the ModelSim transcript console. The test passes if the

following condition is met: All transactions the Source BFM sends to the Single-Clock FIFO buffer match

the transactions received by the Sink BFM.

Setting up the Test

In this section you generate a testbench system in Qsys for the DUT.

Before you run the design file, unzip the

ug_avalon_verification.zip

file to a working directory on your hard

drive. This location is referred to as

.

1. On the Windows Start menu, point to All Programs, then Altera, and click Quartus II>

to run the Quartus II software.

2. On the File menu, click Open. Select st_bfm_project.qpf located in

verification /qsys

.

3. On the Tools menu, click Qsys.

4. On the Qsys File menu, open st_bfm_qsys_tutorial.qsys. This is a blank Qsys system.

5. On the Device Family tab, for Device family, select Stratix V. (You can leave the actual Device unknown.

6. Type

fifo

in the search box located in the Component Library panel. From the search results, double-

click on the Avalon-ST Single Clock FIFO component.

7. In the parameter editor, change the parameter values to match the values listed in the following table.

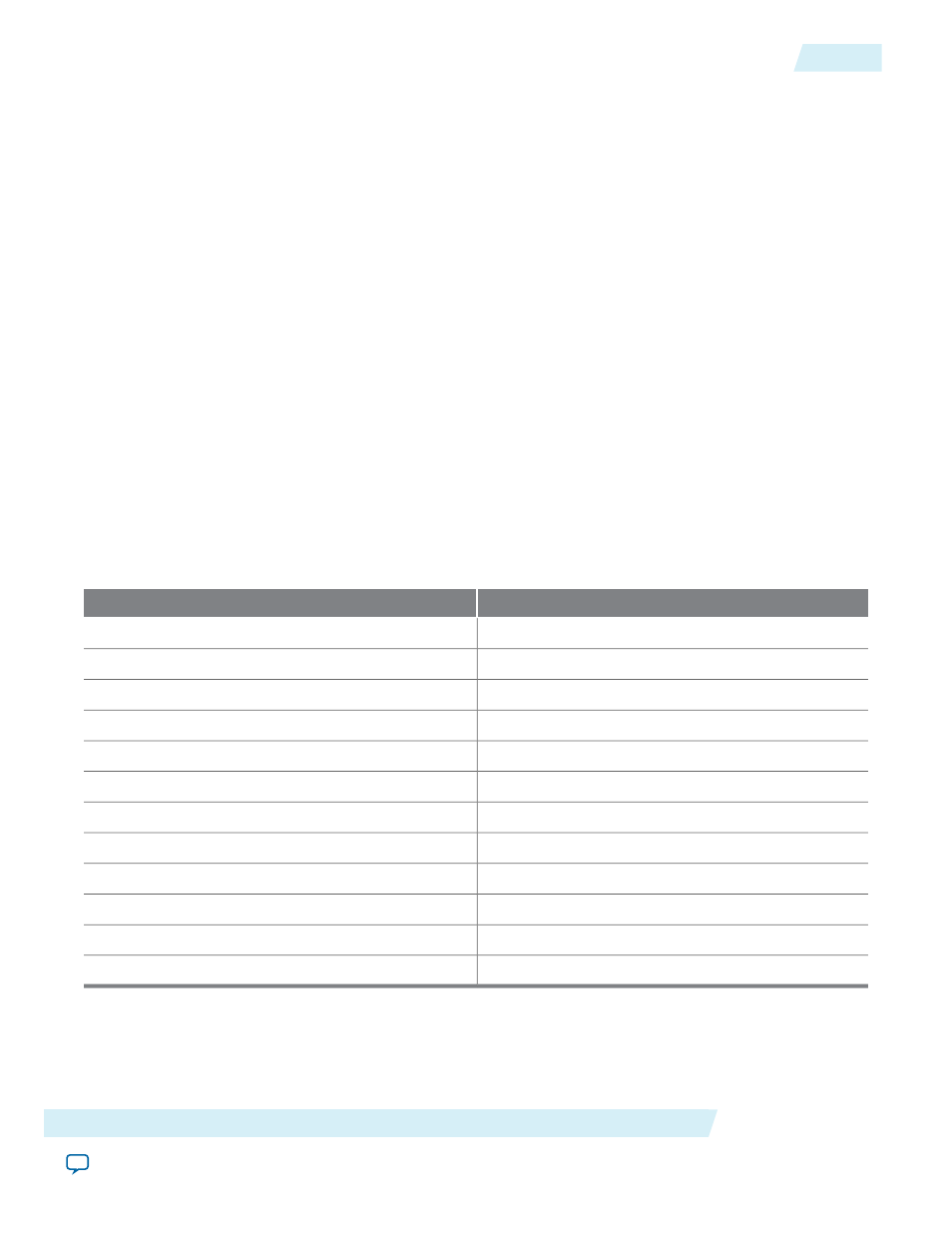

Table 16-1: Avalon-ST Single Clock FIFO Parameter Values

Value

Parameters

4

Symbols per beat

8

Bits per symbol

2

FIFO depth

3

Channel width

3

Error width

On

Use packets

Off

Use fill level

Off

Use store and forward

Off

Use almost full status

Off

Use almost empty status

Off

Enable explicit maxChannel

Off

Explicit maxChannel

8. Click Finish.

9. Right-click on the

sc_fifo_0

component and select Rename. Rename the component to

dut.

10. On the System Contents tab, in the Export column, rename the exported interface names to match the

names listed in the table.

Altera Corporation

Avalon-ST Verilog HDL Testbench

16-3

Setting up the Test