Reset source bfm, Parameters, Reset source api – Altera Avalon Verification IP Suite User Manual

Page 18: Reset source bfm -1, Parameters -1 reset source api -1

3

Reset Source BFM

Send Feedback

The Avalon Verification IP Suite includes a Reset Source BFM that you can use to generate a reset signal in

your testbench.

Parameters

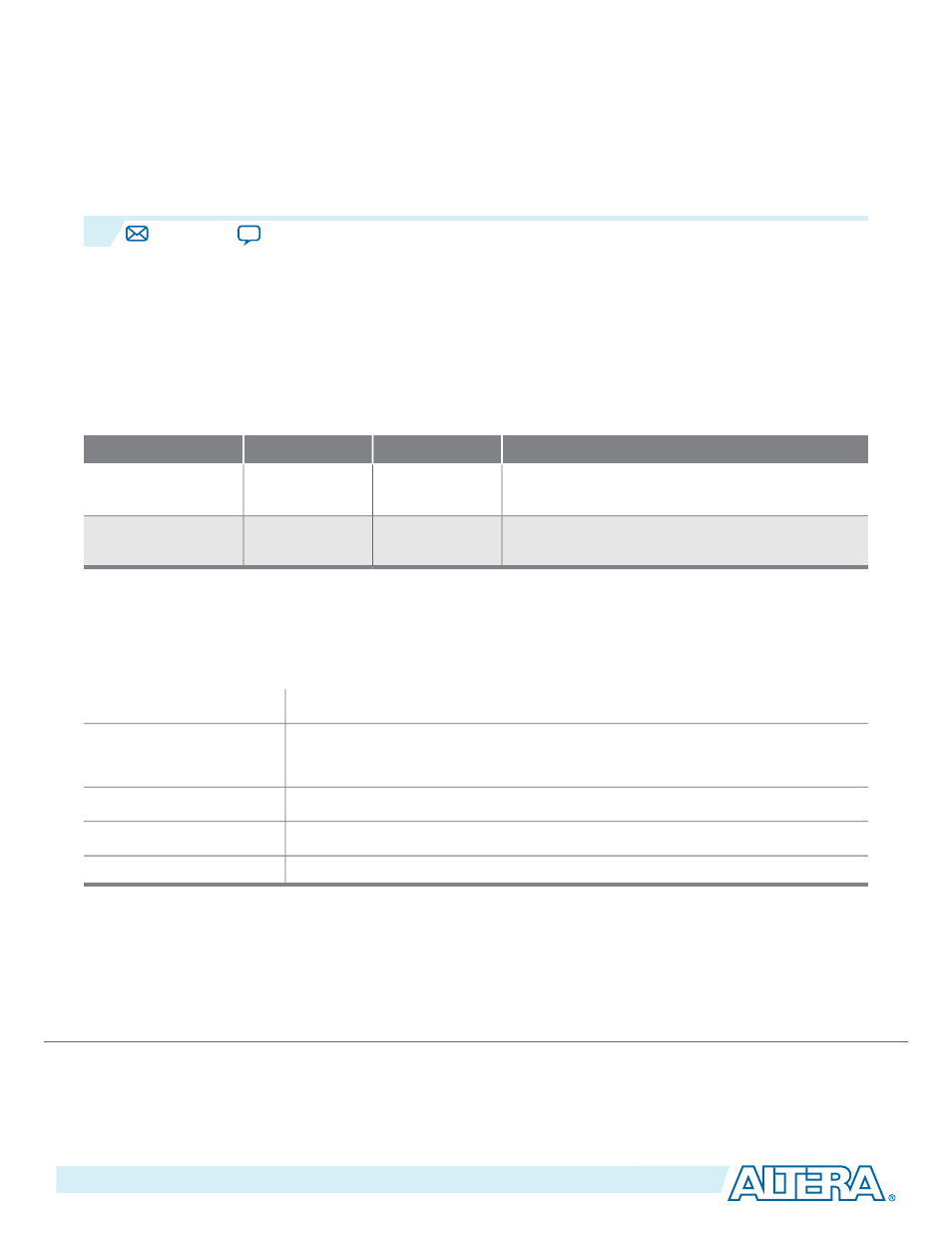

Table 3-1: Reset Source BFM Parameter Settings

Description

Legal Values

Default Value

Option

Specifies the polarity of the reset signal. Turn on

this option to set the reset signal active high.

On/Off

On

Assert reset high

Specifies the number of cycles that the reset signal

is asserted at the initial stage of the simulation.

N/A

0

Cycles of initial

reset

Reset Source API

reset_assert

reset_assert

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void.

Returns:

Asserts the reset signal.

Description:

Verilog HDL

Language support:

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134