Avalon-st source bfm, Timing, Avalon-st source bfm -1 – Altera Avalon Verification IP Suite User Manual

Page 113: Timing -1

8

Avalon-ST Source BFM

Send Feedback

The Avalon-ST Source BFM implements the Avalon-ST interface protocol. The Avalon-ST protocol is

point-to-point, packet oriented, and drives unidirectional data. This BFM component includes a procedural

interface to control signals on the Avalon-ST interface, including: ready, start of packet, and end of packet.

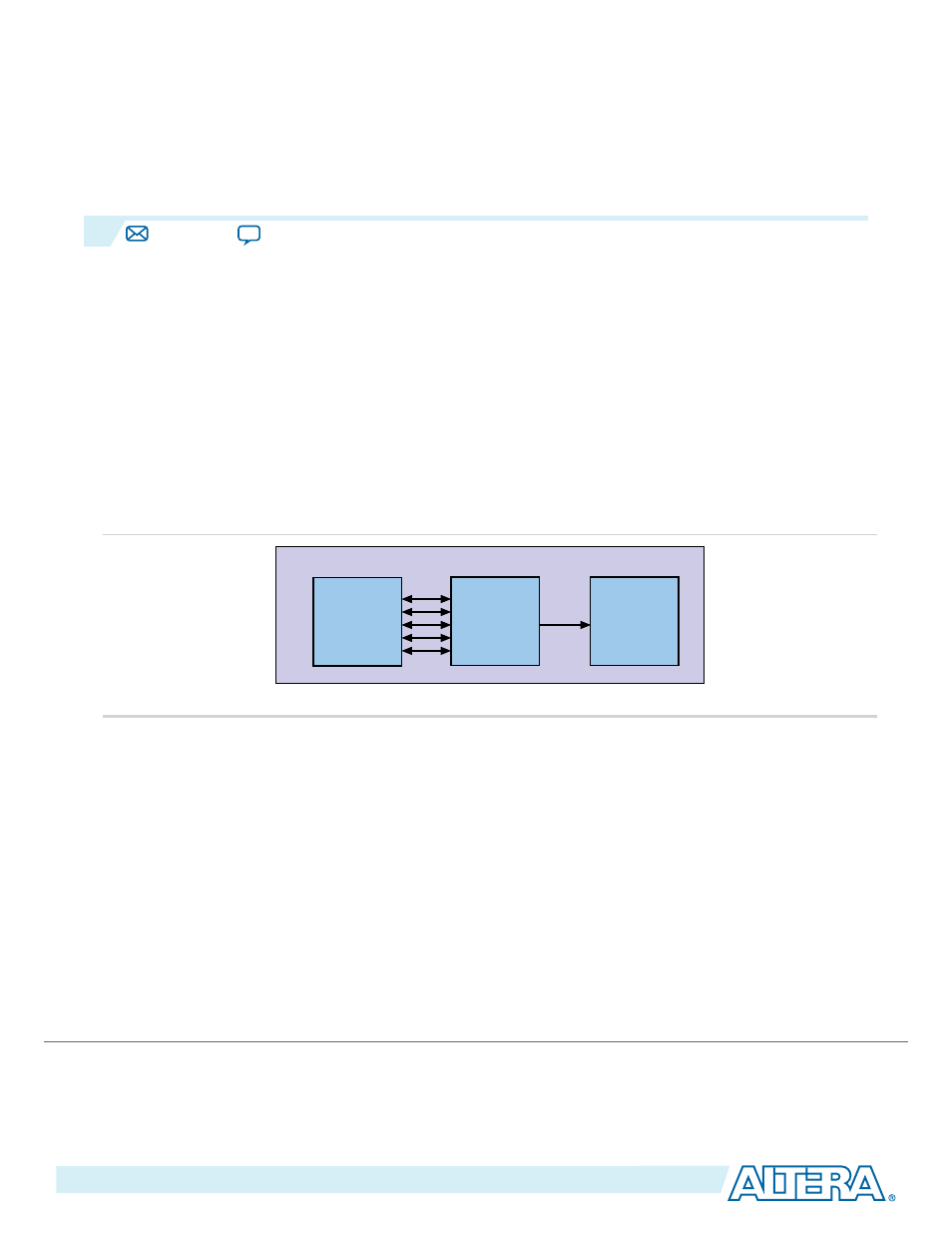

The following figure shows the top-level modules for a testbench. This testbench uses an Avalon-ST Source

BFM to verify an Avalon-ST sink component. In addition to the Altera-provided Avalon-ST Source BFM

component, the testbench typically includes a test program and the DUT.

The BFMs allow illegal transactions so that you can test the error-handling functionality of your

DUT. Consequently, you cannot rely on the BFMs to guarantee protocol compliance. The Avalon

Monitor components verify protocol compliance.

Note:

Figure 8-1: Top-Level Module to Verify an Avalon-ST Sink Device

Avalon-ST

Source BFM

Avalon-ST

Sink Component

DUT

Testbench

API

Function

Calls

Avalon-ST

Test Program

Related Information

Timing

The following figure illustrates the timing for an Avalon-ST Source BFM sending data to a sink. In the first

instance the sink is not ready when the source has data. In the second instance, the sink is ready but the

source does not initially have valid data.

The Avalon-ST BFM behaves differently depending on whether the sink’s

READY_LATENCY = 0

or

READY_LATENCY > 0

. When the ready latency is 0, the source BFM holds its current transaction until

Note:

the sink is ready. When the ready latency is greater than 0, the BFM drives idles until the sink is ready.

Then, it drives the transaction.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134