Avalon-mm vhdl testbench description, Avalon-mm vhdl testbench description -6 – Altera Avalon Verification IP Suite User Manual

Page 216

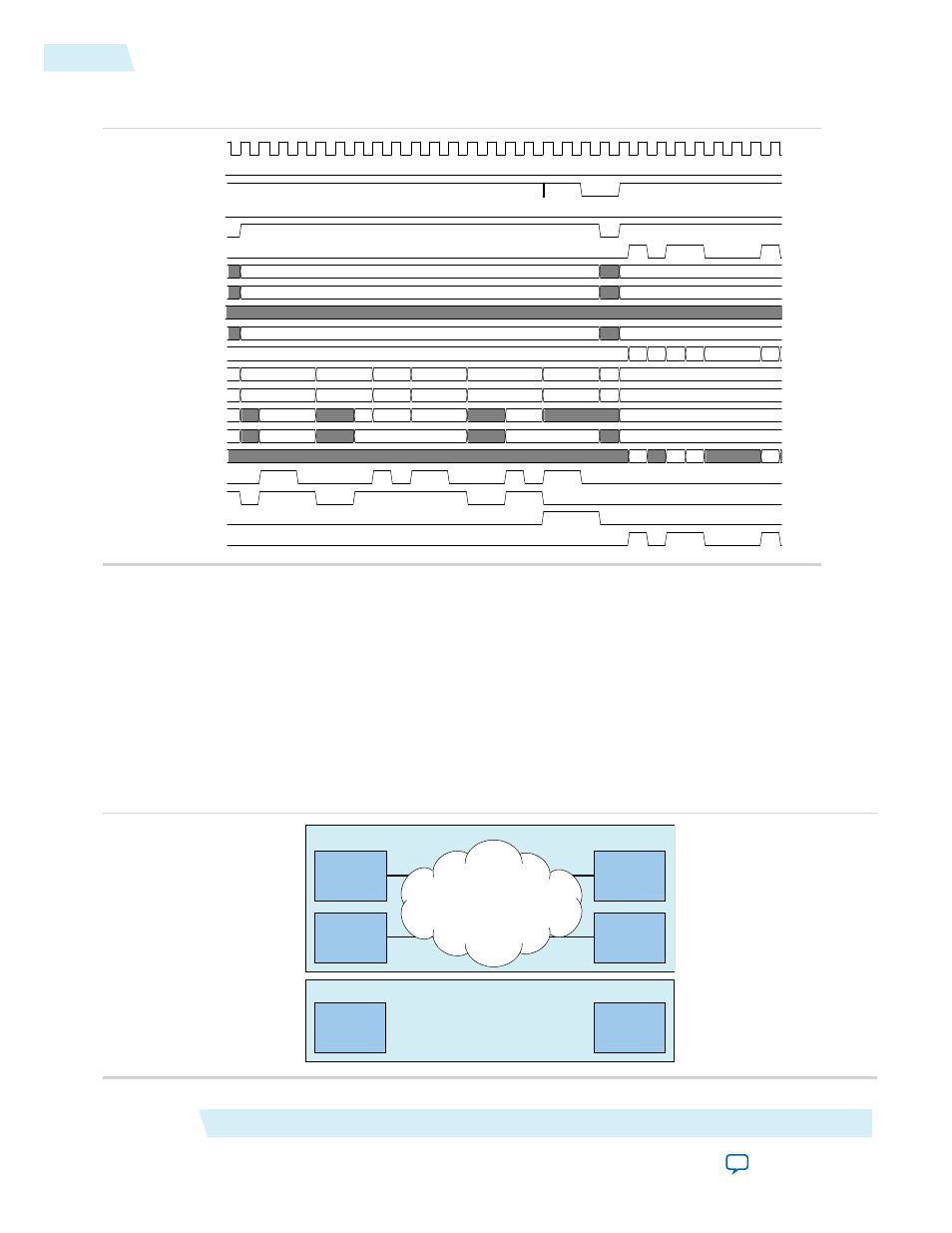

Figure 17-4: Avalon-MM Master0 and Slave0 Reads

..

0F0C

'b

.

116C

4

3

F

F

C .

0 .

7 .

9 .

00000000

3 .

2FD

2FE

2FF

300

301

302

3C3

3C4

5

4

3

2

1

4

3

.

3 .

.

2635FB4C

.

4.

47B9A .

7C6DA9F8

.

DBCD

.

F

F

F

F

C

.

. 7

. 9

.

3

.

tb.clk

tb.reset

m0_waitrequest

m0_write

m0_read

m0_readdatavalid

m0_address[12:0]

m0_burstcount[3:0]

m0_writedata[31:0]

m0_byteenable[3:0]

m0_readdata[31:0]

s0_address[9:0]

s0_burstcount[3:0]

s0_writedata[31:0]

s0_byteenable[3:0]

s0_readdata[31:0]

s0_waitrequest

s0_write

s0_read

s0_readdatavalid

Avalon-MM VHDL Testbench Description

At the top-level, the VHDL HDL version of the Avalon-MM testbench includes two modules:

• The System Under Test- This module includes the Avalon-MM Master and Slaves components and the

Avalon-MM Master and Slave BFMs.

• The Test Program- The module includes Master Command and Slave Threads.

Figure 17-5: VHDL Testbench for Two Avalon-MM Masters and Slaves

Interconnect

Avalon-MM

Master BFM

Avalon-MM

Master BFM

Avalon-MM

Slave BFM

Avalon-MM

Slave BFM

System Under Test

Master

Command

Thread

Test Program

Slave

Thread

Avalon-MM Verilog HDL and VHDL Testbenches

Altera Corporation

Avalon-MM VHDL Testbench Description

17-6