Application programming interface, Application example of bfms, Application programming interface -3 – Altera Avalon Verification IP Suite User Manual

Page 14: Application example of bfms -3

• API communication interface—Bridges the VHDL API to the API handler logic.

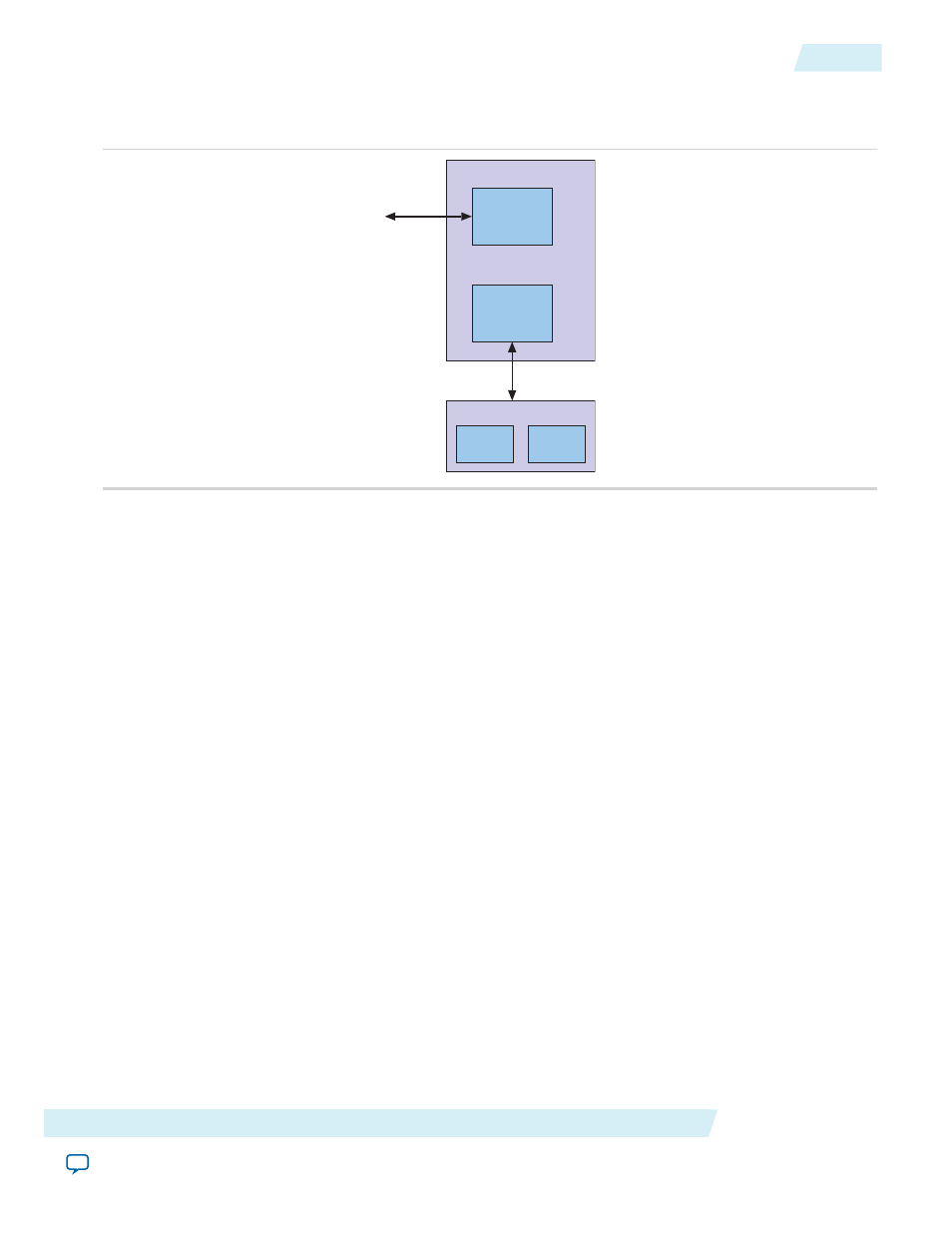

Figure 1-1: VHDL Component BFM

API

Interaction

BFM Interface

VHDL BFM

Communication

Interface

VHDL

Procedures

VHDL

Events

VHDL Package

SystemVerilog

BFM

API Handler

Logic

The monitor components use the SystemVerilog Assertion (SVA) language and are supported only by

simulators that support SVA, including:

• Modelsim-Altera Starter Edition (ASE)

• Synopsys VCS

• Mentor Graphics

®

Questa.

Application Programming Interface

Altera provides you with a set of application programming interfaces (API) for each Avalon Verification IP

Suite BFM. You can use the APIs to construct, instantiate, control, and query signals in all BFM components.

Your test programs must use only these public access methods and events to communicate with each BFM.

You can design custom verification environments that do not take advantage of the API. However,

Altera does not guarantee continued support or backwards compatibility custom methods.

Note:

Application Example of BFMs

The figure below shows an Avalon-MM design with the following components:

• An Avalon-MM device under test (DUT) that includes both Avalon-MM master and slave interfaces

• An Avalon-ST DUT that includes both source and sink interfaces, although typical components might

include a single Avalon interface.

This figure illustrates it is possible to write a testbench using a traditional VerilogHDL implementation or

using SystemVerilog with VMM.

Altera Corporation

Introduction to Avalon Verification IP Suite

1-3

Application Programming Interface