Generating a qsys testbench system, Setting up the simulation environment – Altera Avalon Verification IP Suite User Manual

Page 207

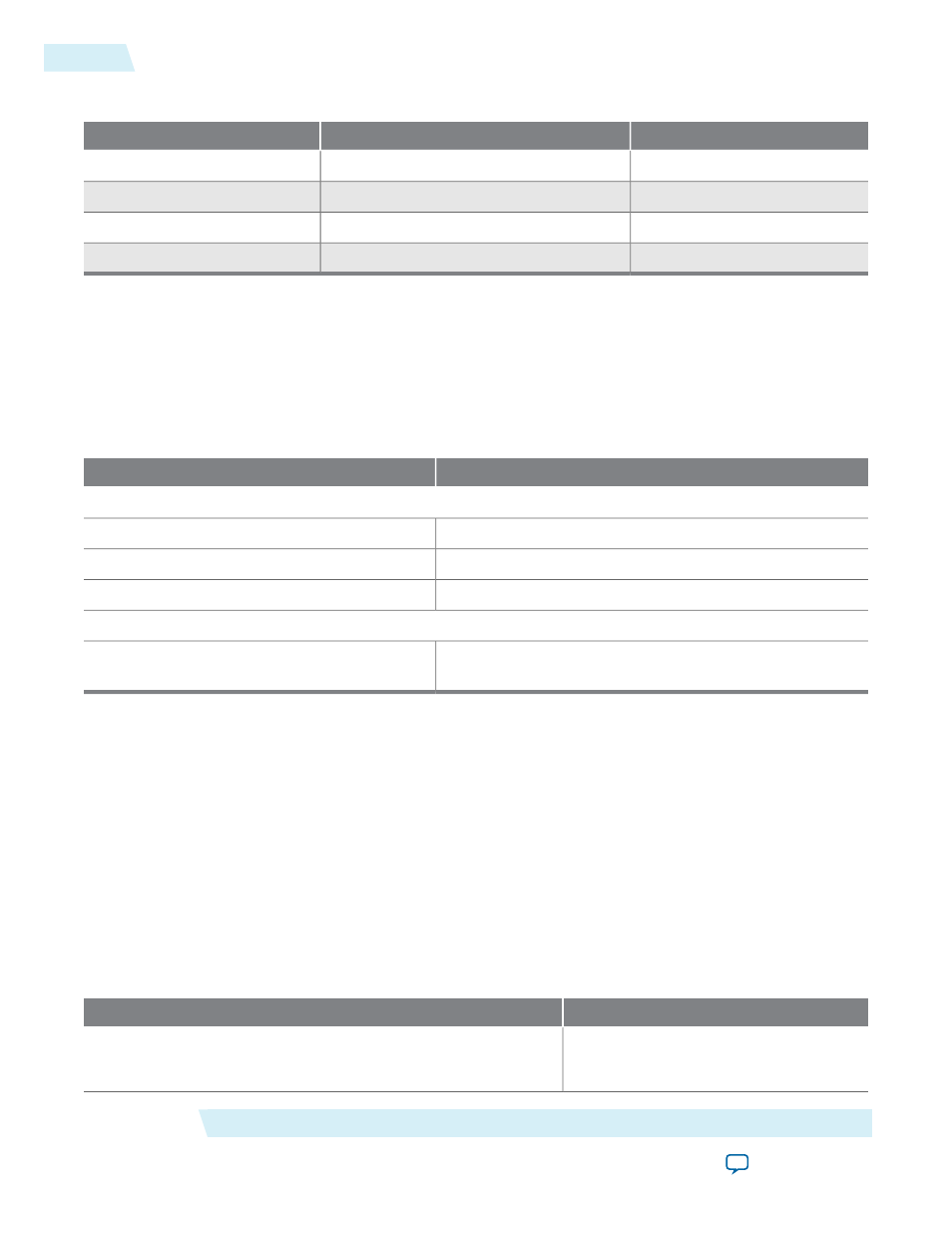

Table 16-2: Avalon-ST Single Clock FIFO Exported Interface Names

Export Name

Description

Interface Name

clk

Clock Input

clk

reset

Reset Input

clk_reset

st_in

Avalon Streaming Sink

in

st_out

Avalon Streaming Source

out

Generating a Qsys Testbench System

Follow these steps to generate a testbench system for the DUT:

1. On the Generation tab, select Generate Testbench.

2. Change the parameter values to match the values listed in the table.

Table 16-3: Generation Tab Parameter Values

Value

Parameters

Simulation

Standard, BFMs for standard Qsys Interfaces

Create testbench Qsys system

Verilog

Create simulation model

Leave this option off

Allow mixed-language simulation

Output Directory

working_directory/ug_avalon_verification /qsys/st_bfm_qsys_

tutorial

Testbench

3. Click Generate. Save the system if you are prompted to do so. Do not close the Qsys window after

successful generation.

The test program for this tutorial is located in

user_test_program

.

Note:

Setting up the Simulation Environment

To set up the simulation environment for your test program, open your ModelSim script file (

.tcl

or

.do

).

Set the hierarchy variables used in the Qsys-generated simulation script (

msim_setup.tcl

). The ModelSim

script file (

load_sim.tcl

) included with this tutorial has the correct hierarchy variable settings. The following

coding examples show how to set up the hierarchical variables used in the Qsys-generated simulation model.

Table 16-4: Coding Examples to Set Hierarchy Variables

Description

Hierarchy Variables Coding Example

Sets the name of the top level file that

instantiates the Qsys-generated testbench

system and the test program.

set TOP_LEVEL_NAME “top”

Avalon-ST Verilog HDL Testbench

Altera Corporation

Generating a Qsys Testbench System

16-4